干掉硅中介層?

本文授權轉載自公眾號“半導體行業觀察”,ID:icbank,作者:L晨光。

近年來,在AI高算力需求推動下,HBM正在大放異彩。

尤其是進入2023年后,以ChatGPT為代表的生成式AI市場的瘋狂擴張,在讓AI服務器需求迅速增加的同時,也帶動了HBM高階存儲產品的銷售上揚。

TrendForce數據顯示,2023年全球搭載HBM總容量將達2.9億GB,同比增長近60%,預計2024年還將再增長30%。SK海力士預測,HBM市場到2027年將出現82%的復合年增長率。

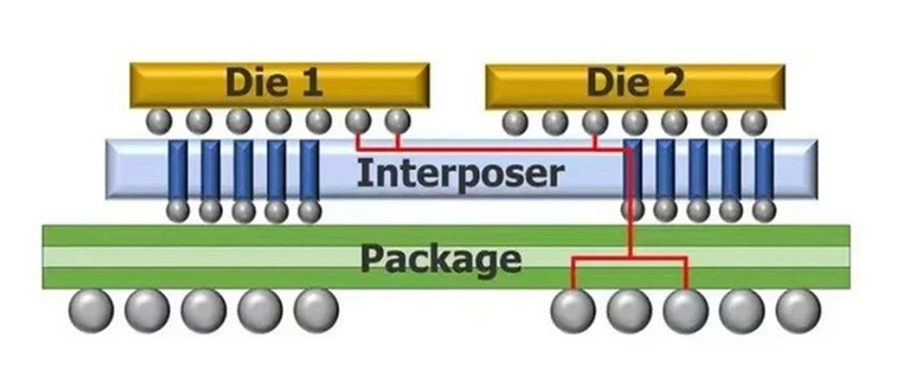

在此發展勢頭下,作為AI芯片的主流解決方案,HBM受到了存儲巨頭的高度重視。自2014年SK海力士首次成功研發HBM以來,三星、美光等存儲巨頭也紛紛入局,展開了HBM的升級競賽,目前HBM已從第一代HBM升級至第四代HBM3,產品帶寬和最高數據傳輸速率記錄被不斷刷新。下一代HBM3E超帶寬解決方案也已在樣品測試階段,HBM4也被提上議程。

▲HBM發展歷程

▲HBM發展歷程

借助AI東風,HBM需求水漲船高,三大原廠紛紛推動HBM新代際產品開發與產線擴張。與此同時,臺積電也宣布將CoWoS產能擴大兩倍,以期更好地支撐水漲船高的HBM需求。

近日,英偉達H200的推出有望再次掀起HBM布局浪潮,未來在AI大模型日趨復雜化的趨勢下,隨著存儲巨頭的持續發力,產業鏈上下游企業也將緊密部署,HBM的影響力將逐步擴大并帶來全新機遇。

關于HBM技術的未來發展路線,在我們之前的文章《HBM 4,要來了》有比較詳細的介紹;以及在《HBM的崛起》、《存儲巨頭競逐HBM》文章中,更是詳細介紹了HBM的前世今生,以及存儲巨頭圍繞HBM的產業布局和規劃。感興趣的讀者可以點擊鏈接自行跳轉查閱。

本文,將圍繞HBM發展過程中的一個細分環節——硅中介層(Si-Interposer),來詳述其價值、瓶頸以及未來的技術走向。

談到硅中介層,我們需要先來了解一下HBM的結構。

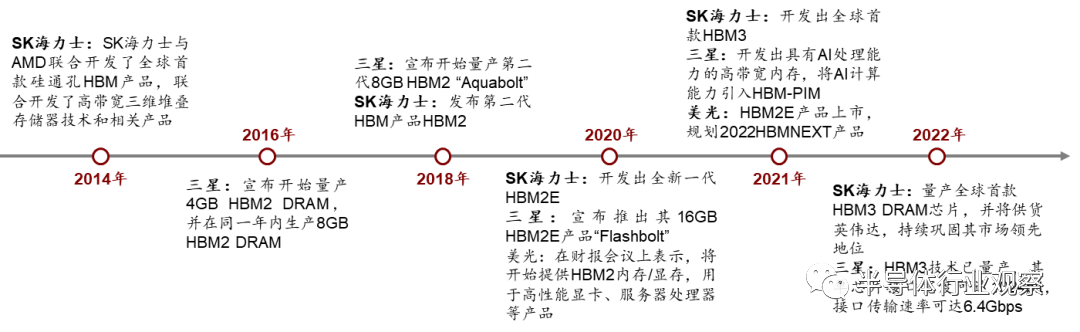

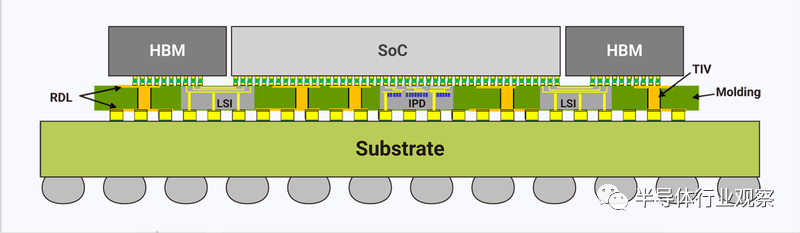

與傳統DDR存儲器不同,HBM使用硅通孔技術(TSV)和微凸塊(ubump)垂直堆疊多個DRAM芯片,并通過封裝基板內的硅中介層與GPU、CPU或ASIC直接相連,從而具備高帶寬、高容量、低延時與低功耗等優勢,相同功耗下其帶寬是DDR5的三倍以上。

因此,HBM突破了內存瓶頸,成為當前AI GPU存儲單元的理想方案和關鍵部件。

▲HBM架構示意圖

▲HBM架構示意圖

HBM是一種標準化的堆棧儲存技術,可為堆棧內部,以及內存與邏輯組件之間的數據提供高帶寬信道。HBM封裝將內存裸晶堆棧起來,并透過TSV將它們連接在一起,從而創建更多的I/O和帶寬。

從上圖可以看到,這個硅中介層可以理解為一塊精密的電路芯片,里面布置了密集的電信號傳輸通道,用于幫助芯片、封裝基板進行電性能互連,實現芯片與芯片,芯片與封裝基板之間的信息交換,可以用于提高芯片的性能和帶寬,以及使芯片更加緊湊,從而減少了信號傳輸的延遲和功耗。

總體來看,硅中介層是一種經過驗證的技術,具有較高的細間距I/O密度和TSV形成能力,在2.5D IC芯片封裝中扮演著關鍵角色。

硅中介層有兩種技術路線,代表分別是臺積電的CoWoS和英特爾的EMIB。

臺積電CoWoS-S通過硅中介層承載處理器和HBM,處理器和若干HBM的投影面積決定了硅中介層的大小,而中介層的面積受限于光刻掩膜尺寸,會限制HBM的使用數量。

這就成為了早期HBM應用的瓶頸——需要HBM的往往是高性能的大芯片,而大芯片的規模本身就已經逼近了掩膜尺寸極限,給HBM留下的面積非常有限。對此,臺積電相繼攻克了多重困難突破了中介層尺寸的限制,單芯片內部逐漸可封裝4顆、6顆,甚至12顆HBM。

硅中介層的面積如此發展,在解決尺寸限制的同時,也帶來了新的挑戰,即成本越來越高。以8GB HBM2為例,其成本約175美元,其中硅中介層成本約25美元,而同時期的8GB GDDR5僅需52美元,在沒有考慮封測的情況下,HBM成本已經是GDDR的三倍左右。

尤其是隨著HBM的演進,中介層面積越來越大,要包含所有的Die,大大增加成本。此外,中介層是有半導體工藝制作,成本不低,且很難做很大面積。

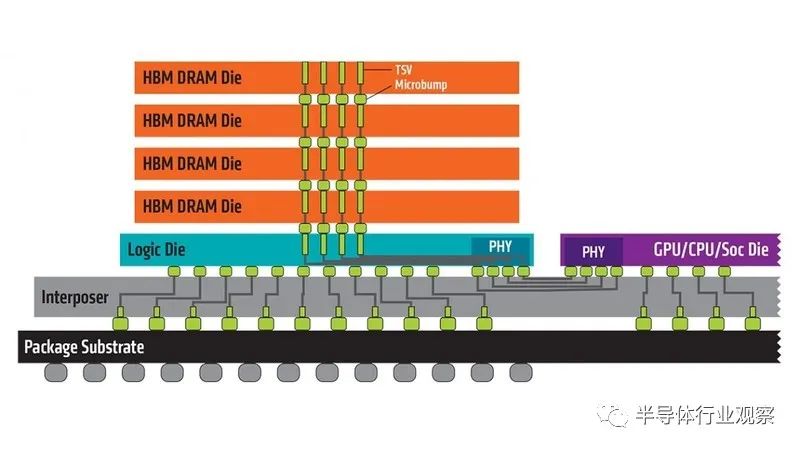

為了降低中介層的成本和尺寸,英特爾發明了EMIB,將die-die的互連用“硅橋(Si Bridge)”實現,且硅橋嵌入在基板內部,die-substarte的連接通過傳統方法實現。這種做法可以大大降低硅中介層的面積,減少成本,減輕多die封裝的限制。

▲英特爾EMIB架構圖

▲英特爾EMIB架構圖

值得注意的是,EMIB通過非常小的凸點間距提供高互連密度,從而允許芯片之間具有更高的帶寬,并且由于走線長度較短,因此比使用有機基板具有更低的功耗。它類似于微型硅中介層,僅覆蓋小芯片之間需要連接的區域。

但是,盡管EMIB充分利用了硅中介層和有機載板的技術特點和電氣特性,但也存在組裝成本高的缺點,因為需要在有機載板中鑲嵌,增加了工藝復雜度,限制了載板的選擇。

因此,為了進一步降低成本,行業廠商開始研究棄用硅中介層的技術和方法。

1、SK海力士:直接在處理器上堆疊HBM4據報道,SK海力士開始招聘CPU和GPU等邏輯半導體設計人員,希望直接在處理器上堆疊HBM4,這不僅將改變邏輯芯片和內存的典型互連方式,還將改變其制造方式。

目前,HBM堆棧集成了8個、12個或16個存儲器件,以及一個像集線器一樣的邏輯層。HBM堆棧被放置在CPU或GPU旁的中間件上,并通過1024位接口與處理器相連。SK海力士的目標是將HBM4堆棧直接放在處理器上,完全省去中介層。

據悉,SK海力士正在與包括英偉達在內的幾家公司討論其HBM4集成設計方法。SK海力士和英偉達很有可能從一開始就聯合設計芯片,并在臺積電生產,臺積電還將使用晶圓鍵合技術把SK海力士的HBM4安裝到邏輯芯片上。為了使內存和邏輯半導體在同一芯片上作為一個整體工作,聯合設計是不可避免的。

臺積電目前也有像SoIC等更高級的3D封裝工藝,確實可以將更好的將顯存堆疊到芯片之上,就像AMD的3D V-Cache處理器就是用到了這種工藝,不過該處理器最大的問題就是發熱,還有良率以及成本等因素,目前還不太適用于HBM顯存。

據業內人士表示,直接連接存儲器和邏輯芯片在經濟上是可行的。不過,雖然將HBM4堆棧直接放在邏輯芯片上可以在一定程度上簡化芯片設計并降低成本,但這也帶來了另一個挑戰——散熱。

散熱本身就是HBM長期存在的挑戰之一,HBM的2.5D封裝結構會集聚熱量,而靠近CPU和GPU的布局又會進一步增加熱量。以Nvidia的H100處理器為例,其消耗數百瓦的功率,并耗散數百瓦的熱能,且HBM內存也相當耗電。

目前來看,如果發熱問題能夠得到解決,HBM的“游戲規則”可能會發生變化,存儲器和邏輯半導體之間的連接可能會變得像一體機一樣運行,而無需中間件。

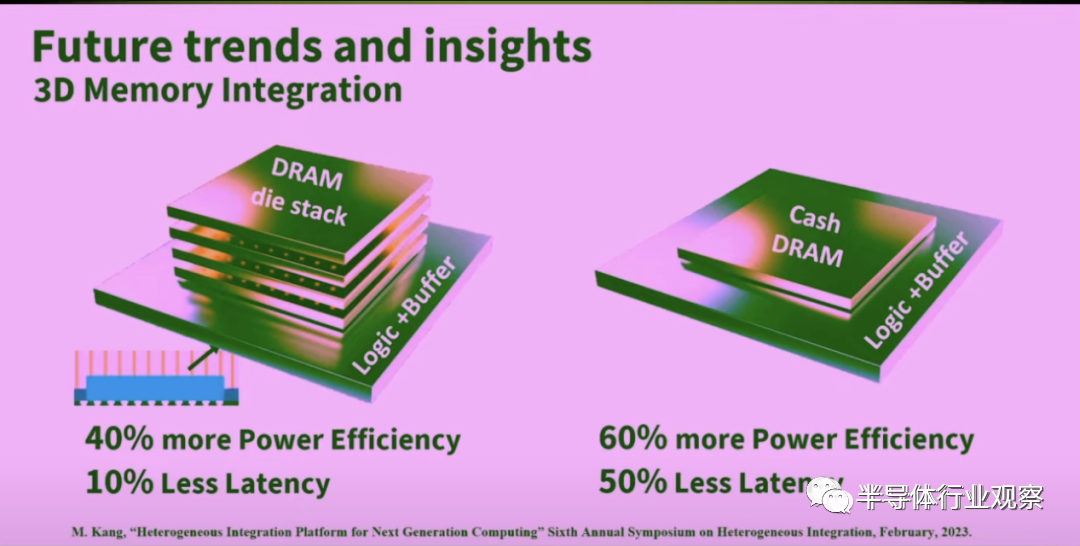

2、三星:將HBM存儲與芯片封裝解耦三星方面也認為,隨著封裝變得越來越大,帶來了裝配和可靠性等多方面的挑戰。為此,三星通過提供一個在logic die上堆疊DRAM die的方法,將功耗效率提升了40%,并將延遲降低了10%。

在另一種方案中,三星將Cash DRAM堆疊在logic die上,使得功耗效率提升了60%,延遲則降低了50%。在三星看來,這是一個更好的、面向未來解決方案。

展望未來,三星方面進一步指出,光互連將發揮重要作用。

在使用光學I/O后,將獲得非常高的帶寬密度;與此同時,這種解決方案還能帶來非常低的功耗。在三星看來,光學I/O將邏輯封裝和存儲封裝連接到一起。

同時,該技術還能將HBM存儲與芯片封裝完全解耦,將HBM模組從芯片本體分離出來,并通過光學技術與邏輯處理單元相連。這樣就不必處理中介層帶來的芯片封裝復雜性,且這種方法簡化了HBM和邏輯單元的芯片制造與封裝成本,并且避免了復雜的數字到光學信號內部轉換。

隨著全球存儲巨頭的深度介入,上述挑戰或將得到解決,HBM市場的激戰也會愈演愈烈。

除了存儲原廠之外,臺積電等廠商也正在通過研發不同類型的中介層,或是采用不同的材料來實現成本節降。

以臺積電為例,臺積電正在不斷嘗試降低下一代HBM的成本,宣布擁有多種不同類型的中介層:除了硅中介層外,還有RDL中介層,以及其他試圖擺脫中介層的技術探索。

比如CoWoS-R、CoWoS-L等,前者將硅中介層換做有機RDL,能夠降低成本,不過劣勢是犧牲了I/O密度;后者是臺積電專門針對AI訓練芯片設計的,結合了臺積電CoWoS-S和信息技術的優點,預計晚些時候才能應用。

▲圖源:TSMC官網

▲圖源:TSMC官網

此外,集成扇出封裝技術(INFO)也正在考慮集成HBM,作為硅中介層的經濟替代方案等等...。Cadence IP團隊產品營銷總監Marc Greenberg表示,如果行業能夠聚集在一起并決定一個適用于標準封裝的內存標準,那么就有可能提供與HBM類似的帶寬,且成本要低得多。

可見,棄用硅中介層或進一步降低成本正在成為HBM未來新的技術創新路線。成本因素之外,HBM干掉硅中介層還可以減小傳輸路徑、提升傳輸速率,體積也會更加小。

在HBM棄用硅中介層的跡象之外,Chiplet也正在進行此方面的探索(其實某種程度上,HBM就是Chiplet的一種類型)。

迄今為止,業界領先的Chiplet互連需要先進封裝和昂貴的硅中介層。而Eliyan公司驗證了他們在高性能Chiplet互連方面的突破。

筆者在此前文章《Chiplet,怎么連?》中對此有過詳細介紹。

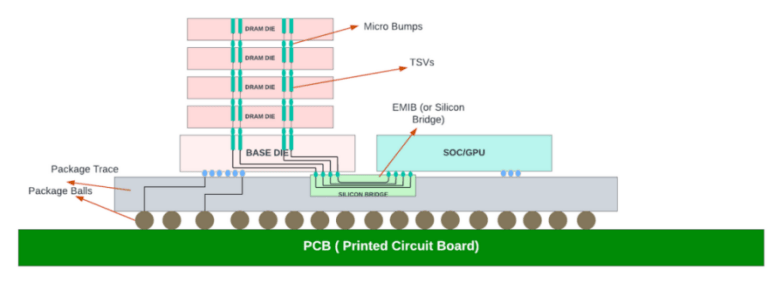

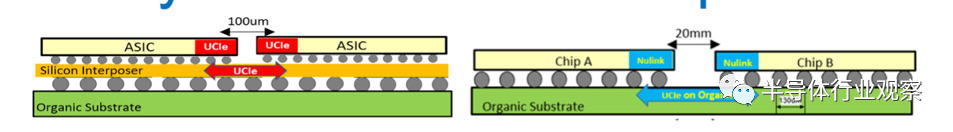

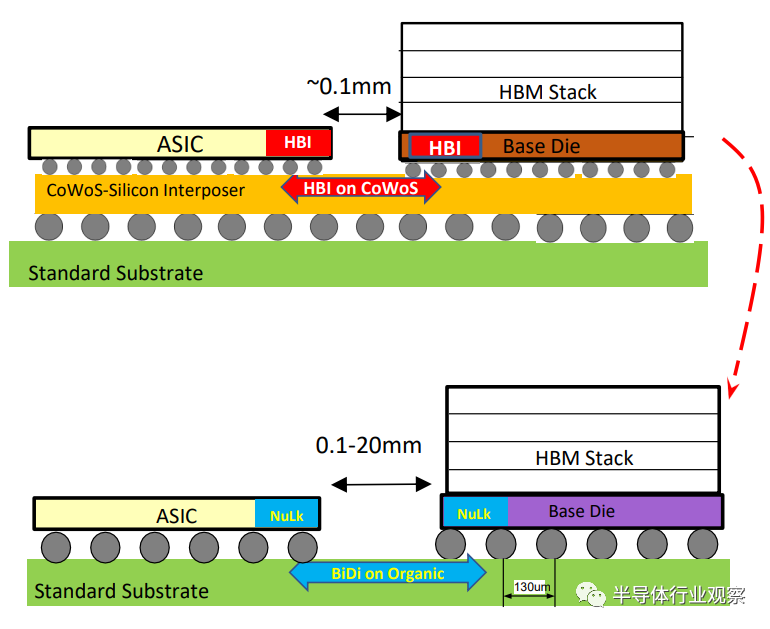

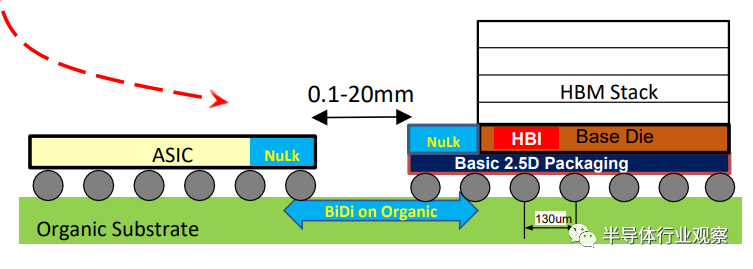

Eliyan憑借其Nulink技術,可以為die-to-die互聯在各種封裝襯底上提供功耗、性能和成本的優勢方案。因為這種PHY接口可以讓不同的裸片直接在有機襯底上實現高速互聯,而不必采用CoWoS、EMIB或硅中介層等昂貴的先進封裝方式,在降低成本的同時加速產品制造周期。

從上圖可看到,左邊是當今常見的使用硅中介層的Chiplet互連方法;右邊是Eliyan的NuLink技術,可以以卓越的帶寬實現小芯片互連,而無需硅中介層。

可見,NuLink通過簡化系統設計降低了系統成本。更重要的是,Eliyan可以增加芯片之間的距離,對于生成式AI,NuLink為每個ASIC提供更多的HBM內存,從而提高了配備HBM的GPU和ASIC的內存密集型應用程序的性能。

▲采用硅中介層的傳統Chiplet解決方案與采用有機基板的Eliyan Nulink

▲采用硅中介層的傳統Chiplet解決方案與采用有機基板的Eliyan Nulink

Eliyan還展示了其NuLink PHY的第一個工作芯片,該芯片采用5nm標準制造工藝實現,可以讓Chiplet與不同工藝的裸片實現混搭,不需要硅中介層等先進封裝技術。

▲NuGear消除了對大型硅中介層的需求

▲NuGear消除了對大型硅中介層的需求Eliyan指出:“如今業內的一大需求是能夠獲得足夠大的中介層,這樣就可以構建越來越大的GPU或TPU,并帶有大內存。”

這還是在拋開成本因素的考量下,而Nulink有機基板的尺寸可以達到硅中介層的三四倍,同時提供相同或更好的功率效率和帶寬。這導致成本更低、制造速度更快,每個封裝的計算能力更強。

與此同時,NuLink還為HBM DRAM提供卓越的散熱性能,消除了HBM-ASIC之間的熱串擾,允許ASIC時鐘速度提高20%,以及更簡單/低成本的冷卻。

測試和產量是另一個優勢。傳統硅中介層需要使用微凸塊將小芯片連接到中介層引線,微凸塊限制了對晶圓進行全面測試的能力,使良率面臨風險。

對此,Nulink對有機基板的使用通過允許使用具有標準尺寸凸塊的小芯片來緩解這個問題,這可以更有效地進行測試。因此,可以將芯片良率從60%提高到90%左右。

總結來看, Eliyan消除了對先進封裝的需求,例如Chiplet設計中的硅中介層尺寸有限、成品率低、成本高、難以冷卻、供應鏈有限、測試等所有相關限制和復雜性。NuLink技術能夠實現DRAM擴展、節約材料成本、提高產量并縮短芯片上市時間等優勢。

Eliyan認為,其Chiplet互連產品可以超越英特爾和臺積電等芯片巨頭的先進封裝技術,或者有望成為英特爾、臺積電的最佳選擇,從而實現下一波高性能芯片架構。NVIDIA、Intel、AMD和Google等公司可以授權NuLink IP,或從Eliyan購買NuGear小芯片,以消除硅中介層尺寸限制帶來的性能瓶頸,使他們能夠實現更高性能的AI和HPC SoC。

但任何技術都有兩面性,并非提供完全的優勢。例如,Eliyan新技術可以把Chiplet從2.5D的封裝要求切換到2D上,但必然需要增大線速來換取更低的線密度需求。但速率的增加對于PHY的設計會引入顯著的額外延時和能耗。

總的來說,無論是HBM、Chiplet異構集成,還是裸片堆疊,這些先進封裝技術正逐步解決傳統芯片縮放遇到的難題,同時也為未來的芯片設計提供了更多的靈活性和高效性。

同時隨著互連技術的演進,預計將進一步促進HBM或Chilet封裝技術的進步,為行業帶來更低功耗、更高性能以及更低成本的解決方案。

無論是哪種技術,都各有優劣,也永遠面對新的瓶頸和挑戰,需要根據實際需求來進行設計和選擇。但萬變不離其宗,持續提升性能、降低成本,無疑是行業發展永久的“必殺技”。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。