基于ARMS和FPGA的嵌入式數控系統設計

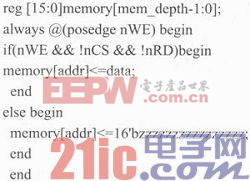

3.2 FPGA端SRAM實現

ARM和FPGA的通信需要的接口信號有地址線A0-A15、數據線D0-D15、片選信號nCS,讀信號nRD和寫信號new,每次需要實現16位數據的讀寫。用Verilog硬件語言描述SRAM時序如下:

可知只有在片選信號、讀信號都拉低而寫信號仍為高的情況下,才在data線上輸出地址線上對應單元的數值,其他情況下FPGA都將data線置為高阻態,放棄對data線的控制。

4 基于FPGA的DDA精插補器設計

隨著FPGA器件及其開發技術的日臻成熟,采用FPGA實現運動控制的方案顯示出巨大的潛力。由于FPGA的設計是并行的、多線程,而且具有在線可編程能力,兼備了速度快和成本低的優點,同時克服了專用處理器靈活性方面的不足。基于FPGA的DDA精插補器相對傳統的軟件插補具有強大的優勢。

4.1 數字積分插補算法

目前比較成熟的數控插補算法有逐點比較法、最小偏差法和數字積分法等,數字積分法又稱數字微分分析器(Digital Differential Analyzer,DDA)。采用該方法進行插補,具有運算速度快、邏輯功能強、脈沖分配均勻等特點,可實現一次、二次甚至高次曲線插補,易于實現多軸聯動。

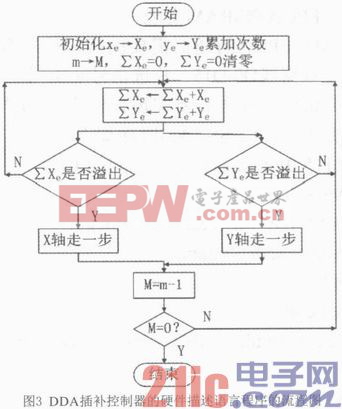

數字積分插補算法是將函數的積分運算轉換成變量的求和運算。如果所選擇的脈沖當量足夠小,則用求和運算代替積分所引起的誤差可以不超過允許的數值。采用兩個寄存器(函數寄存器和累加寄存器)和一個全加器構成數字積分器,將單位周期選得足夠小,每單位周期都向累加器累加函數寄存器中的數值,如果累加器溢出,就向外發送脈沖,實時地改變函數寄存器的值,就可以完成步進電機的調速。DDA插補控制器設計的硬件描述語言程序的流程圖如圖3所示。本文引用地址:http://cqxgywz.com/article/148022.htm

4.2 數字積分插補的FPGA實現

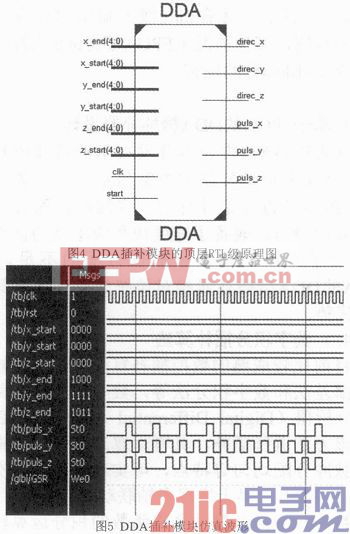

采用有限狀態機的設計方法,每個軸的數字積分插補均由一個三狀態機的積分累加器完成。本系統的FPGA開發環境為Xilinx公司的Xil inx ISE,并結合ModelSim仿真軟件對整個系統進行了全面的功能驗證。如圖4所示為DDA插補模塊的頂層RTL級原理圖,由圖5可知DDA插補模塊的輸入信號為各軸的起始坐標以及時鐘信號和啟動信號,輸出信號為各軸的脈沖信號和方向信號。

運用ModelSim仿真軟件對DDA插補模塊進行仿真驗證。測試數據的起點坐標為(0,0,0)終點坐標為(8,15,11),仿真結果如圖5所示,顯示系統很好的完成了三軸的脈沖分配。

fpga相關文章:fpga是什么

c語言相關文章:c語言教程

評論