一種自適應波束形成算法實現

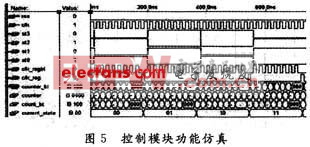

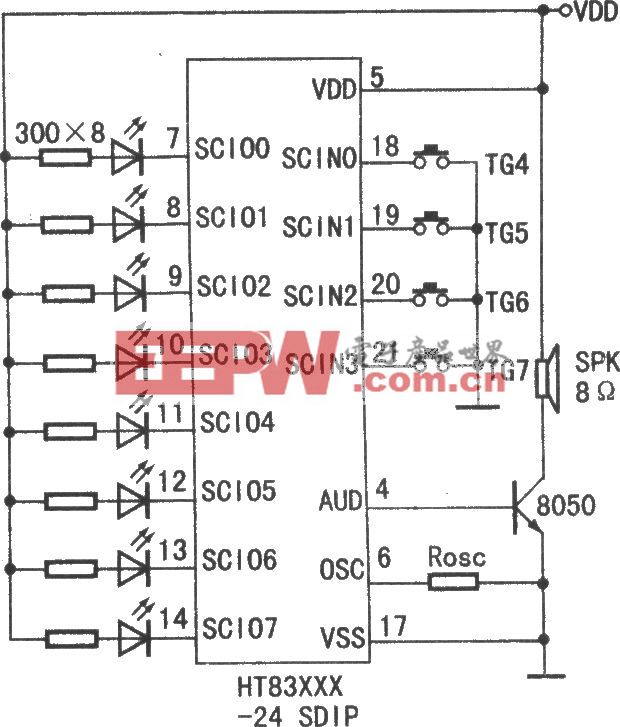

輸入信號和權值是8位的復數數據,通過控制模塊選擇乘法操作的操作數,兩個復數信號相乘的4種組合00,11,01,10可以完成實部和虛部之間4個乘法運算,四種情況控制模塊輸出的控制信號分別為ST0,ST1,ST2,ST3。

其中,clk_regbt用來控制乘法器完成乘法,counterbt用來控制乘數的位選,clk_reg用來控制運算新數的進入、上次計算的完畢和結果的輸出。

2.2.2 存儲模塊

一種存儲模塊,它包括:用于根據外部指令/地址信號來產生內部信號的指令/地址寄存器,且所述的指令/地址寄存器件帶有一個輸出晶體管;被分成第一和第二兩組的多個存儲器件;用于連接所述的指令/地址寄存器件和所述的存儲器件的布線;和用于安裝所述的指令/地址寄存器件和所述的存儲器件的基板;所述的布線包括:從所述的指令/地址寄存器件延伸至第一個分支結點的第一段布線;從第一個分支結點延伸至第二個分支結點的第二段布線;從第一個分支結點延伸至第三個分支結點的第三段布線;從第二個分支結點分出延伸至所述的第一組存儲器件的第四段布線;和從第三個分支結點分出延伸至第二組存儲器件的第五段布線;和所述的指令/地址寄存器件包括:阻抗調節器,用于調節從所述的指令/地址寄存器件和第一段布線之間的連接點看去所述的指令/地址寄存器件的輸出阻抗,通過調節該阻抗調節器,可使所述的輸出阻抗在內部信號的工作電壓范圍內基本保持不變;和上升時間/下降時間調節器,用于將內部信號的上升時間和下降時間調節至特定值。

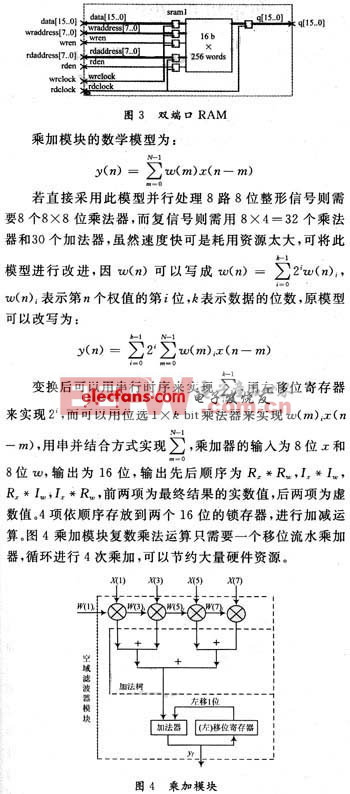

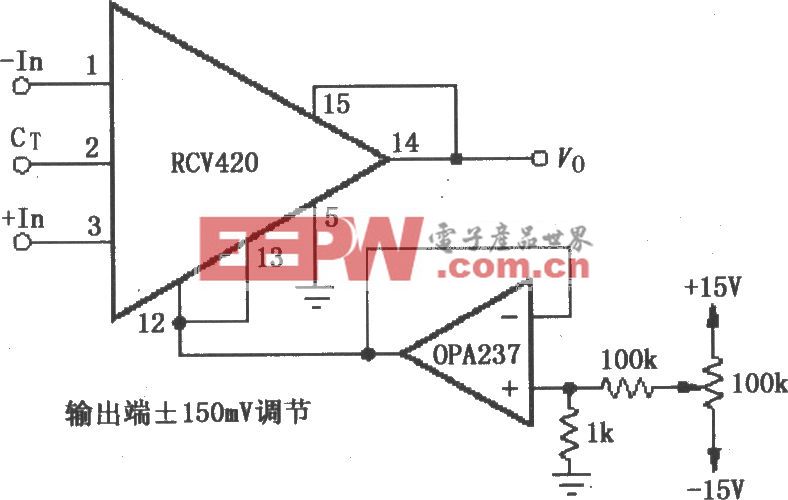

存儲模塊采用8位和16位雙口RAM(如圖3所示)作為信號數據和權值數據的存入和讀取存儲器,分別用來存放輸入信號x、權值ω和誤差e,分別由控制信號clkregbt,clk_regw和clk_rege來控制信號的寫入和讀出。其中x_ram用來存放輸入信號;w_ram存放權值,其輸入為系數更新模塊的輸出,輸出為更新后的權值。

2.2.3 自適應處理及復數乘加器模塊

數字波束形成器是通過加權因子對空間不同陣元接收信號的加權求和而成的。由于加權因子相當于濾波器系數,而輸入的信號為空間位置不同的陣元的接收信號。所以可將數字波束形成器等同于一個空域濾波器來實現。

3 系統仿真與驗證

本文設計核心部分是基于Stratix系列EPlS10芯片設計的分別對I/Q兩路原始數據進行DLMS自適應算法和復數乘加運算,在QuartusⅡ環境下用VHDL語言編寫了各功能模塊,并進行了仿真,共占用了2 703個邏輯單元,同時應用Matlab對數字結果進行波形仿真,以下為仿真驗證的結果。

圖5為主控模塊的仿真波形,其中ST0,ST1,ST2,ST3為復數乘法的4種組合,clk_regbt用來控制乘法器完成乘法,counter_bt用來控制乘數的位選,clk_reg用來控制運算新數的進入、上次計算的完畢和結果的輸出。

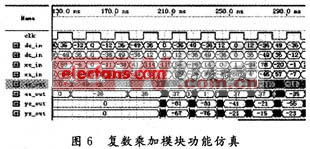

圖6為復數乘加模塊功能仿真結果,dc_out,ds_out,xc_out,xs_out分別是輸入信號和期望信號的實部和虛部,ec_out,es_out,yc_out,ys_out分別為誤差和濾波輸出的實部和虛部。

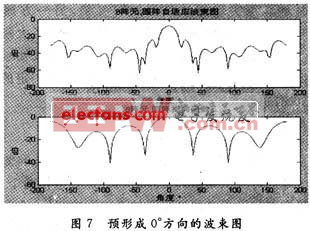

圖7為系統仿真測試結果:系統預形成波束方向為0°方向,干擾從45°傳來,通過仿真結果可以看出,主波束在0°方向形成,和預形成主波束吻合,在45°干擾方向形成零陷,并且提高了主波束的增益,滿足系統的設計要求。

4 結 語

本文介紹了利用FPGA芯片實現的自適應BDF結構,給出了相應的硬件設計和仿真驗證,采用FPGA結構,硬件成本低,在自適應陣列信號處理系統中具有很好的應用前景。

評論