一種片內硬件調試支持單元設計

1.2 Trace Buffer

為了實現引言中提到的調試的可觀察性,本系統中就必須具備能夠記錄總線通信信息以及指令執行情況的模塊。AHB Trace Buffer就是一個循環緩沖存儲體,被用來存儲AHB上通信的所有信息。AHB總線上的地址、數據和各種控制信號存儲在其中,并且可以在以后的分析中讀出;同時在需要調試寫入的時候也可以通過AHB寫總線寫入數據。本模塊因每個周期需記錄的信息位寬為128 b,所以設計的AHB TraceBuffer存儲器將采用4個位寬為32 b的同步SRAM構成,深度可配置。若整個Buffer的容量為1 KB,則每一個SRAM大小為64×32 b,若容量為2 KB,則每一個SRAM大小為128×32 b,依次類推。

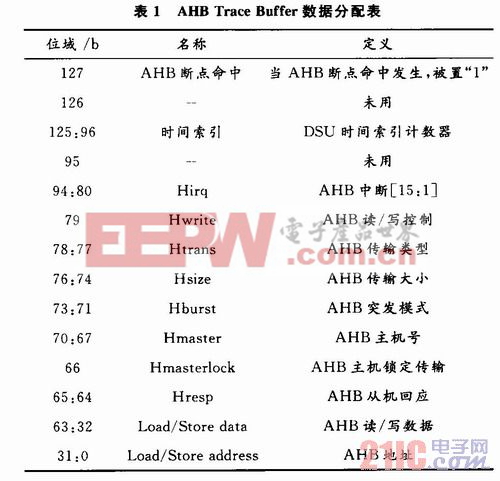

在正常總線通信中,每一筆AHB傳輸將被循環存儲到Buffer中,在處理器進入調試模式后,AHB TraceBuffer被暫時掛起,這時可由外部調試設備利用AHB總線訪問Buffer,通過地址譯碼控制4塊SRAM各自的使能信號,進而完成讀/寫操作。Buffer的數據輸入端為128 b,包含的有地址、數據、控制信號和控制寄存器值等,詳細見表1。本文引用地址:http://cqxgywz.com/article/150984.htm

同樣在微處理器內部實現一個指令TraceBuffer,用來存儲執行過的指令。該部件同樣循環存儲,位寬128 b,利用4塊SRAM構成。該存儲器中將記錄指令執行過程中指令運行狀態,操作碼、操作數和操作結果,以及PC指針等值,用以方便以后讀出進行診斷定位。

兩塊Buffer在系統正常運轉時記錄數據,所以為了保證其內容的正確性,僅允許系統進入調試模式時對其進行讀寫訪問,而正常狀態下將禁止對其訪問。

1.3 DSU單元

對于嵌入式系統而言,其內部的大部分信號與微處理器的工作狀態對于開發者都是不可見的,本設計就是通過提高在系統開發過程中用戶對系統的可觀察性和可控制性從而幫助開發者更為有效的定位設計中的錯誤,從而加速開發周期。為此,本系統必須在片上集成單獨的調試單元用于監測系統運轉并能接管處于異常狀態時的微處理器。

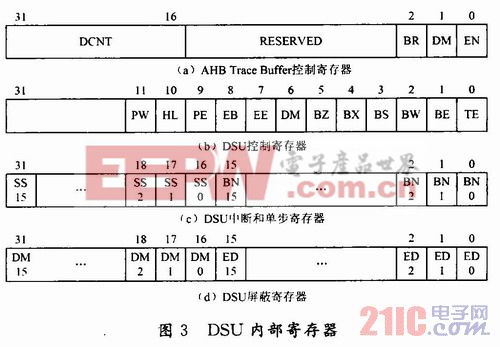

借鑒CPU中程序狀態字的作用,DSU中首先需要一些寄存器能夠控制與管理整個調試單元的行為,它應該能接收來自調試主機發布的調試命令,同時也能夠對系統內部斷點等觸發行為做出實時響應以及在任何時刻都能被調試主機所訪問,為此,該調試單元設計了如圖3所示的部分關鍵寄存器。

圖3(a)為AHB Trace Buffer控制寄存器。其中EN位將控制AHB Trace Buffer的使能;DM位表示Buffer處于延遲計數模式,設計這種模式是為了方便觀察斷點發生前后定長時間內系統的運轉狀態;BR位則表示AHB斷點命中;高16位DCNT表示在延遲計數模式下的延遲計數值。AHB斷點寄存器有兩路,可寫入30位的精確斷點地址,當AHB地址總線上廣播的地址與該斷點地址相吻合時,將會立即凍結AHBTrace Buffer,同時清除AHB控制寄存器的使能位。如果控制寄存器中的延遲模式被置位,那么在斷點命中的同時,將啟動內置自減計數器,該計數值將由DCNT域控制,當計數器自減至零時才能引起凍結行為。

圖3(b)為DSU控制寄存器,它與程序狀態字作用相似,能夠直接控制微處理器的行為模式,決定微處理器如何進入調試狀態。TE位將控制處理器中指令Buffer的使能;第1~5位將作為處理器能夠被掛起的條件位,BE表示處理器發生錯誤可進入調試模式,BW表示觸發IU監測點可進入調試模式,BS表示執行斷點指令(tal)可進入調試模式,BX表示任何陷阱可進入調試模式,BZ是在特定陷阱才能進入調試模式;DM將用來指示處理器進入調試狀態;EE位和EB位為只讀,將記錄DSU外部使能和調試信號;PE位用來記錄處理器是否進入錯誤狀態;HL位記錄處理器是否暫停;PW位記錄處理器是否進入省電模式;其他位均未定義。

圖3(c)為DSU中斷和單步寄存器,由于該系統設計的AHB總線系統最大可支持16個主設備,所以這里的中斷和單步控制寄存器以及屏蔽寄存器也將能夠控制16個主設備。當前面所述的引起系統進入調試模式的條件觸發時,則相應的BNx(break now)位將被置位,而SS(single st-ep)位則可通過外部寫入而使得處理器執行單步操作,這些位將直接驅動對應每一個微處理器的控制部件,由各處理器負責監測并做出相應的調試反應,如PC現場保護、凍結流水和定時器、關閉看門狗等。

圖3(d)為DSU屏蔽寄存器,考慮在多處理器系統中一個處理器進入調試對其他處理器的影響,特設計此寄存器。EDx表示一個處理器進入調試模式時,處理器x是否強制進入調試模式;DMx表示處理器x是否屏蔽其他處理器進入調試模式。當某一處理器因觸發斷點或滿足。DSU控制寄存器所設定的條件時,調試單元內部的屏蔽邏輯將會查詢該寄存器,對其中的EDx和DMx進行相與運算,得出的結果將直接寫入DSU中斷和單步寄存器中對應BNx位,由此可直接決定其他處于正常狀態的處理器是否連帶進入調試模式。

評論