基于 TMS320DM6446 的 H.264 編碼器的設計與優化

2 對DSP數據搬移的優化

視頻編碼需要處理較大的數據量,如一幀CIF格式的YUV數據約有150KB,而H.264除了要存儲當前幀的信息外還必須存儲重建幀和參考幀的信息,為此必須使用DM6446的片外存儲器,也即DDR。但是DSP的CPU對不同的存儲器的訪問速度是不一樣的,訪問速度最快的是離DSP核最近的L1P和L1D,其次是二級緩存L2,訪問速度最慢的是DSP的片外存儲器。DSP對不同的存儲器的訪問速度相差數倍。為了提高編碼器的運行效率,節省DSP核對各個模塊訪問所消耗的時鐘周期,需要啟用DSP的DMA作為數據在兩個存儲器之間的傳輸通路。DMA的的特點是可以在不需要CPU干預的情況下,在后臺執行數據的高速傳輸,能夠有效減輕CPU的負荷。

C64x+在外部存儲器與內部存儲器之間的數據傳遞可以通過增強型DMA(EDMA)實現。EDMA傳輸的發起方式有三種,包括手動觸發方式、外設事件發起方式及QDMA模式。在編碼算法中,每處理完一組宏塊就要向CPU提出DMA傳輸申請,因此采用QDMA模式的傳輸發起方式更適用于編碼算法。

DSP核對兩級內部存儲器L1和L2的訪問速度也不同,如果將外部存儲器的數據直接通過EDMA傳入L1D和L1P,這樣的傳輸方式雖然較快,但需要分配比較大的L1 SRAM,這意味著L1的Cache就會變小,過小的L1 Cache會影響L2和外部內存中的代碼和數據的效率。出于上述考慮可以將L2作為L1與外部存儲器之間的數據過渡區。L1和L2之間的數據傳遞采用C64x+新引入的IDMA,其原理跟EDMA相似,實現兩個內部存儲器的高速數據傳遞。

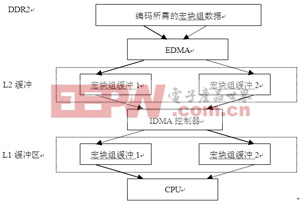

為了使EDMA可以不間斷的實現數據的搬移,本文采用了二級乒乓傳輸的方式,首先在L1 SRAM和L2 SRAM中開辟兩個緩沖區,CPU在處理一個當前宏塊組數據之前先處理EDMA和IDMA的傳輸申請,當CPU編碼完一個宏塊組時IDMA已將數據搬移至離核最近的L1緩沖區,當CPU繼續處理下一個宏塊組前再次處理EDMA和IDMA的傳輸申請。如此以乒乓傳遞的方式搬移數據可以保證CPU處理數據時最短的等待時間。圖4為L1、L2及外部存儲器DDR2之間的數據傳入示意圖。

圖4 存儲器數據傳遞流程圖

3 優化結果及分析

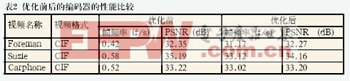

表2為優化前后的H.264編碼器對三個測試序列在DM6446上編碼后的結果比較。在表2中,優化后的幀頻率比優化前有了較大幅度的提高,這是由于對編碼器的運動估計模塊進行優化后,有效減少了這一模塊所消耗的時鐘周期。而對DSP數據搬移方式的優化,減少了DSP核等待數據搬入所消耗的時鐘周期。表中PSNR的值在優化前后并沒有明顯變化,說明優化后編碼質量未受大的影響。

結束語

本文結合DM6446的硬件結構特點,將H.264編碼器在DM6446中成功實現,并對編碼器運動估計模塊及DSP在編碼時的數據搬移進行了優化,取得了初步的效果,基本可達到CIF格式序列的實時編碼要求。由于DM6446具有DSP和ARM9的雙核構架,ARM端負責對整個視頻解決方案的控制和對編碼算法的調用,因此,下一步的工作重點為實現在ARM端對優化后的編碼算法進行合理的調用和控制。

評論