高速并行RS解碼器

3.3 改進的流水線結構

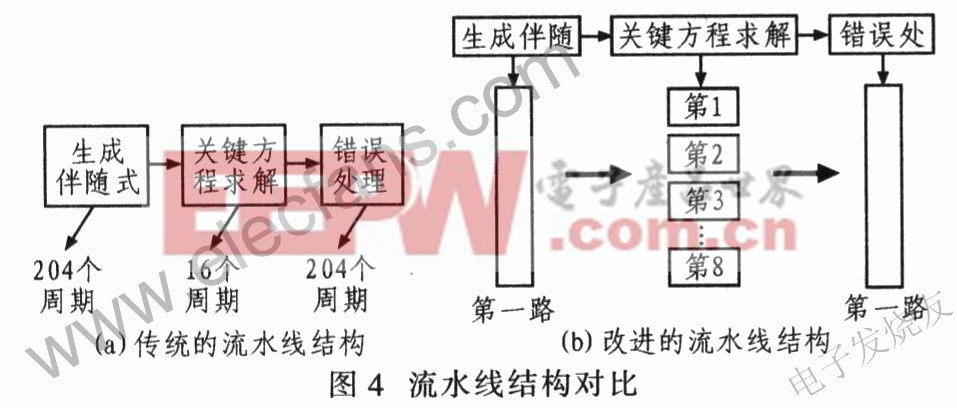

圖4給出了傳統和改進的流水線結構對比。傳統的流水線結構各模塊處理周期差距很大,約達8:1比例,造成周期極大浪費。改進的流水線結構則采用時分復用,可在相應的處理周期不變的情況下可將并行處理的數據率提高到原數據率的8倍。

4 FPGA仿真測試

在OuatusⅡ5.O平臺上采用Verilog編寫編解碼器代碼,測試步驟為:分析與綜合;生成功能網表;配置輸入信號波形;功能仿真;整體編譯;時間仿真。

4.1 系統性能測試

(1)資源利用率綜合功能仿真和時間仿真的編譯報告,系統占用資源詳細情況如表1所示。

(2)解碼數據率解碼數據率=每幀數據的字節數×解碼頻率/系統所需周期。采用Ahera公司的RS解碼器的IP器件,使用CycloneⅡ器件,其解碼數據率為104 Mb/s。由該設計的時序仿真表明解碼器8路復用后的解碼數據率高達116.65 Mb/s。

(3)糾錯能力及糾錯仿真糾錯能力由碼型、解碼算法、控制信號、時鐘等因素共同決定,該設計的單路數據輸入解碼器最大糾錯能力為7字節/204字節(每幀數據204字節,糾正隨機錯誤7字節),接近RS碼的糾錯上限8字節/204字節。8位輸入數據發生錯誤:02H~09H變成了01H,經系統糾錯得到正確的輸出波形。

4.2 系統構造

(1)查表法代替復雜的求逆單元為了獲得更高的解碼速率,使用更少的FPGA資源,系統設計使用標準基到復數基的變換與逆變換,用復數基進行乘法器設計,除法器設計是把處理數據從標準基轉化為指數冪的表示形式,改用高效查表法代替復雜的求逆單元,將σ(x)的逆單元按照尋址方式轉換為表格形式,在程序中直接調用,簡化設計,提高了解碼頻率。

(2)并行流水線結構 由于傳統設計是利用SC模塊求解伴隨式,KES模塊求解關鍵方程,CESS模塊求解錯誤位置和錯誤值,它們之間的處理周期差距很大,造成周期的極大浪費。而采用時分復用的流水線結構可有效解決這一問題,對結構簡單的模塊進行復用,在處理周期基本不變的情況下,從而提高并行處理的解碼數據率。

5 結語

RS編解碼器應用于諸多系統,例如:在數據傳輸鏈路應用中,可在SAN DHB和SAN Target上安裝高速并行RS解碼器,提高遠距離光纖存儲系統的可靠性;將RS糾錯碼應用于突發錯誤率較高的網絡,并與高速的RAID的存儲體系相結合,彌補由于使用RS編碼器產生的延遲,從而實現網絡存儲系統的安全性和高速性。

矢量控制相關文章:矢量控制原理

評論