基于NiosⅡ的嵌入式高速邏輯分析儀

5 結束語

本設計通過在 Cyclone芯片中嵌入軟 CPU、數字 PLL、FIFO和 UART,實現了單片式 8路高速數字信號分析儀。可用鍵盤改變采樣速率,滿足對不同速率的數字信號進行采樣;用點陣式 LCD顯示所采集的 8路數字信號;也可通過串口將采集的數據傳輸到 PC機進行存儲、處理和顯示。本設計的時鐘頻率昀高可 250MHz(CycloneⅡ芯片所支持的昀高工作頻率),從而可以對 8路波特率為 50Mbs的數字信號進行采集與顯示。

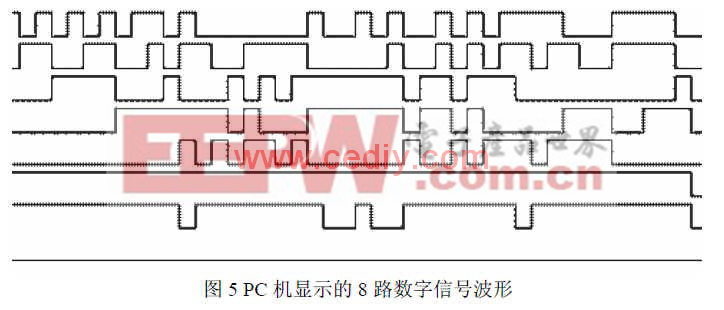

圖 5是通過嵌入式邏輯分析儀采集后,通過串行通信口送到 PC機,在 PC機屏幕上顯示的 8路數字信號實拍照片。

本文引用地址:http://cqxgywz.com/article/152384.htm

本文引用地址:http://cqxgywz.com/article/152384.htm

評論