RS通信編碼器的優化設計及FPGA實現

利用ISE9.0仿真軟件得到的運算一級模二運算的仿真圖如圖2所示。

生成的一級模二運算模塊如圖3所示。

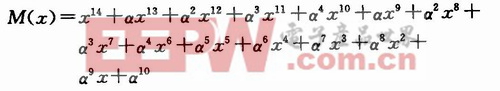

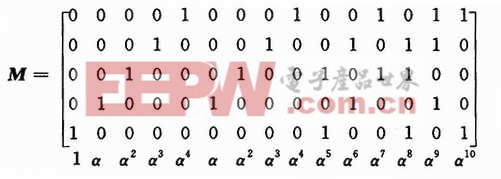

依次連接多個模二運算模塊,進行一步步模二運算,得到余數多項式的系數,即為RS校驗碼。圖4為當信息碼字為M時的RS編譯結果。

可看到此時:

4 FPGA實現

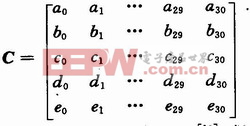

通過RS編碼后的數據為5×31的矩陣,形如;

將5行數據交織編碼,交織度為I=5,得到(ao bo co do eo a1 b1 c1 d1 e1…a30 b30 c30 d30 e30)的形式,利用示波器從串口讀出,得到波形圖如圖5所示。

5 結語

給出的RS編碼器設計方法對生成多項式進行了優化,使得ROM中需要存入的乘法表大幅減少,模擬模二運算的步驟設計編碼過程,最終燒入FPGA中,利用示波器采集到了正確的數據,證明RS編碼器編碼正確。本文介紹的RS編碼器設計方法簡單,占用資源少。

評論