聲導航自行小車研究

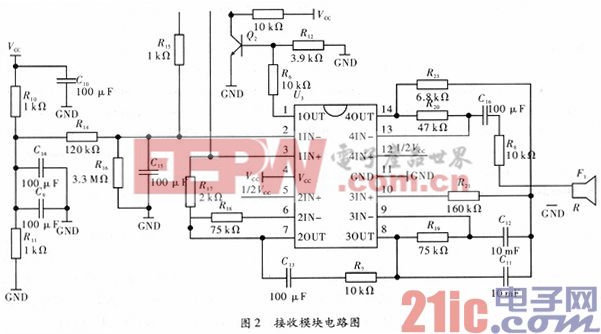

1.2.2 聲接收及硬件濾波模塊

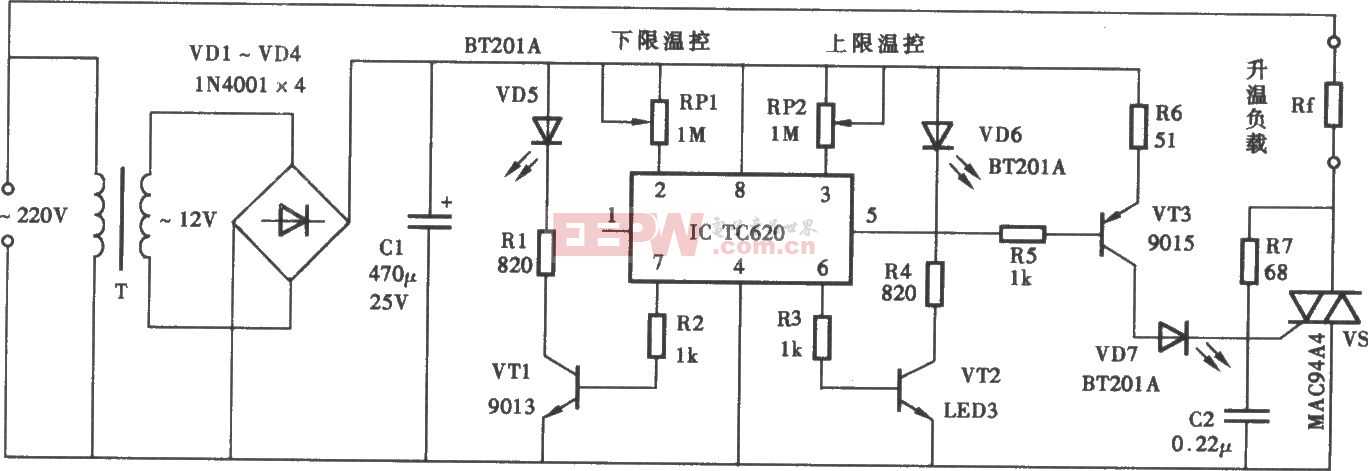

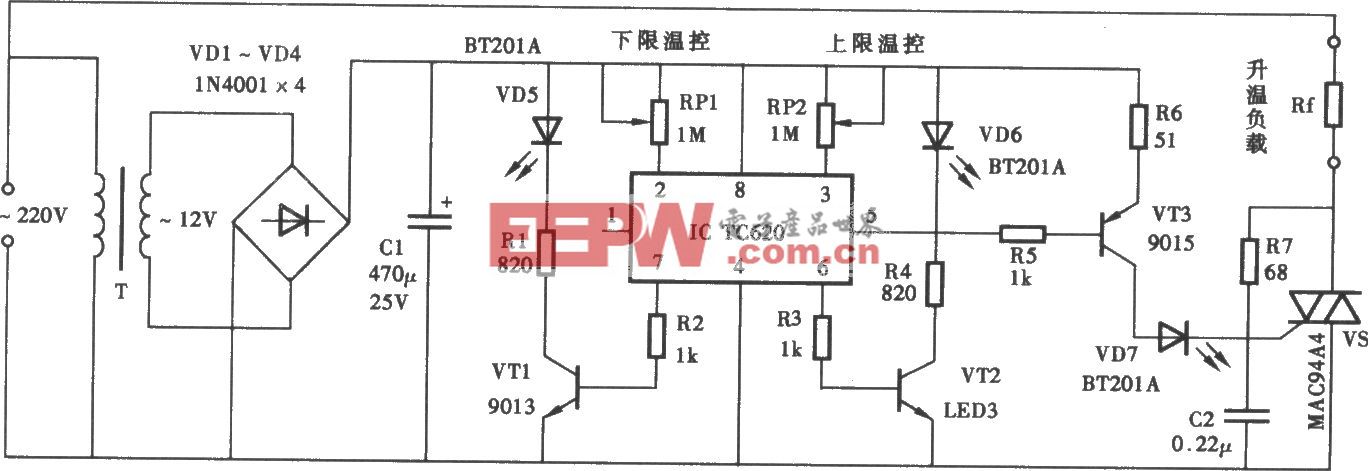

該模塊也采用SRF05超聲波傳感器作為系統的通信模塊,作為接收端,沒有使用發射功能。接收端接收信號后,通過硬件濾波,判斷是否為有效信號。圖2為接收模塊的電路圖。若接收到40 kHz的信號電路導通,I/O口Echo輸出高電平、OUT端輸出1;若接收到的信號中沒有40 kHz的信號電路不導通,I/O口Echo為低電平、OUT端為0。該系統使用了3個接收端,其位置關系如圖3所示。本文引用地址:http://cqxgywz.com/article/170534.htm

1.2.3 FPGA計算時間差模塊

模塊采用Altera FPGA CyclonelI EP2C5T144計算時間差。信號接收端1接收到有效信號后觸發FPGA的計數器,接收端2接收到有效信號后停止計數且觸發另一個計數器,接收端3接收到有效信號后停止計數。計數數值乘以FPGA的頻率可以得到兩個時間差。

1.2.4 單片機模塊

采用飛恩卡爾智能車芯片MC9S12XS128。該芯片接收到FPGA傳來的兩個時間差,再利用麥克問距、聲速算出聲源距離小車的距離r和角度α,并產生合適的PWM驅動電機使小車準確到達聲源處。

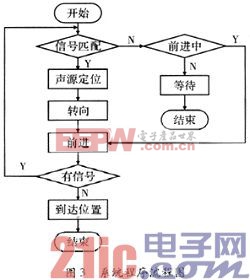

2 軟件設計

圖3為系統程序流程圖。

評論