蘭州重離子加速器小功率直流電源數字化方案

4 調節板硬件程序設計

FPGA是數字電源控制系統中的核心器件,用于實現電流的PID-PWM,決定了電源輸出電流質量。圖4為設計的FPGA硬件程序模塊結構。本文引用地址:http://cqxgywz.com/article/175716.htm

4.1 PID計算模塊硬件程序設計

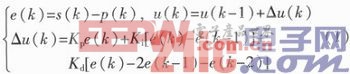

該設計采用增量型PID控制,即:

式中:s(k)為k時刻AD電流采樣值;p(k)為電流給定值;e(k)為電流偏差;Kp,Ki,Kd分別為比例、積分、微分系數;△u(k)為PID變化量;u(k)為PID調節器計算結果。

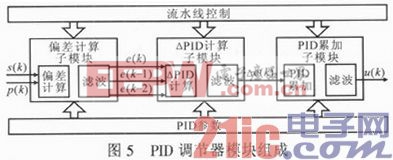

上式中3個式子由硬件程序中偏差計算、PID累加和△PID計算子模塊實現,如圖5所示。

在PID模塊中引入了兩個調節參數,即:積分項上限和PID變化量上限,積分項上限用于防止積分飽和,實現積分分離;PID變化量上限用于限制PID跟蹤速度,從而避免超調。這兩個參數由用戶從CAN總線由上位機輸入。

為適應電源調試的需要,該系統設計了開環、P調節、PI調節和PID調節4種調節方式。在P調節時,忽略積分項和微分項;PI調節時,忽略積分項;開環時,不進行PID調節。為保證計算速度,PID調節器采用流水線設計,3個子模塊依次執行。同時,為避免模塊計算中的中間結果被帶入下一個模塊,引起計算結果干擾,在各模塊中加入了濾波程序。經過仿真,3個模塊可實現預定計算功能。

4.2 PWM硬件程序設計

PID計算數值經變換后得到PWM脈寬量,送入PWM波形發生模塊。當PWM計數器計數小于計算得PWM脈寬量時,輸出低電平;反之輸出高電平。該控制系統使用15位PWM計數器循環計數,計數時鐘系統頻率為50MHz,則PWM輸出波形頻率fs=1.526kHz。設計時將V4導通角滯后V1180°(電流為正極性時),負極性時V3滯后V2180°,從而實現橋口輸出波形倍頻,圖6為PWM輸出波形。故H橋橋口輸出的波形頻率為3.052 kHz。

PWM使能條件:①狀態板無故障送入,狀態板有使能信號送入調節板FPGA;②電源收到CAN總線發來的電源開機命令。使能時PWM開始計數,產生PWM波形,否則波形封鎖,恒輸出低電平。

5 CAN總線通訊網絡

該設計使用Basic CAN協議,采用11位識別碼。電源狀態板和調節板分別作為CAN總線兩個獨立節點,但共用同一識別碼(電源編號),故理論上一臺上位機最多控制2 048臺電源,可滿足需求。圖7為CAN總線網絡。在狀態板中,MCU C8051F自帶CAN控制器,MCU直接或通過索引方式訪問CAN寄存器,實現CAN總線收發和MCU與CAN控制FIFO的數據交換。在調節板中,采用專用CAN控制器芯片SJA1000來通訊,編寫基于FPGA的SJA1000驅動程序來接收SJA1000中斷信號和實現FPGA訪問SJA1000寄存器,實現數據收發。SJA1000驅動程序包括初始化、接收、發送、故障處理和溢出處理等5個子模塊。CAN通信中波特率均為50 kbps,可實現最遠1.3 km的有效通訊。

6 實驗

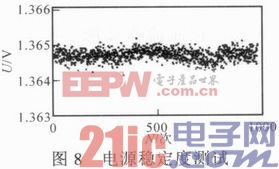

將該電源數字控制方案用于±15A/15 V單H橋DC/DC電源實驗平臺,經調試輸出電流達到預期的±15 A要求。測試電源輸出電流穩定度,負載采用1.25 Ω阻性負載,加電流6.5 A,用7081數字電壓表測量反饋電阻兩端電壓U,如圖8所示。N為采樣次數(每4 s采樣一次,共采樣1 000次),電源穩定度可達6×10-4,達到設計要求。

7 結論

狀態板加調節板的設計可有效分散危險,防止單一控制芯片失效導致電源失控,提高了電源可靠性;基于FPGA硬件程序的電源PID-PWM方式,相比嵌入式軟件實現方式,可防止因軟件執行中中斷響應時間不可控導致的調節實時性問題,增加電流跟隨精度;設計更加靈活,占用資源少,相對基于FPGA的軟核嵌入式軟件實現方式,該設計可減少FPGA資源占用量至原來的1/6左右。

評論