一種多通道ARINC429總線收發容錯方法的研究

3 ARINC429總線接收模塊設計

ARINC429總線接收模塊,要實現能自動識別兩種速率100 Kb/s和12.5 Kb/s,并對數據進行校驗。

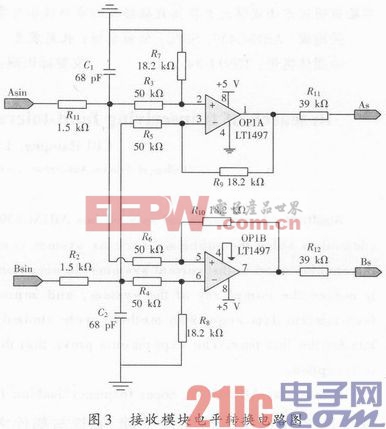

3.1 電平轉換電路

和發送模塊類似,接收模塊在接收信號之前,也要進行電平轉換,將信號轉換成FPGA能識別的電平,ARINC429接收模塊電平轉換電路圖如圖3所示。本文引用地址:http://cqxgywz.com/article/175788.htm

3.2 接收狀態轉換

接收模塊主要有5個輸入端口和2個輸出端口,輸入端口分別為:時鐘clk_800khz、復位rst_n、校驗方式set_od、ARINC429總線busa和busb,輸出端口包括:輸出數據outdata、輸出使能done_rec。

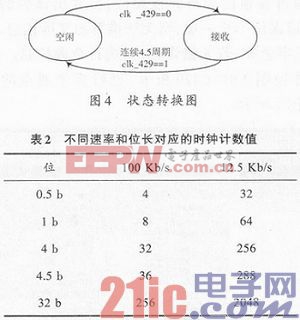

接收模塊主要包括兩個狀態:空閑和接收。在空閑狀態時,ARINC429總線上沒有數據傳輸時,兩根線busa和busb都為邏輯“0”,即clk_429=0時,說明有數據到來,轉到發送狀態。

在接收狀態時,接收數據并移入移位寄存器,當有連續4個周期busa和busb都為0,即clk_429=1時,表示接收完成,轉到空閑狀態。然而,在傳送最后一位數據時還有半個位周期clk_429=0,所以實際上是連續4.5個位周期如圖4所示。由于ARINC429總線有兩種發送速率即12.5 Kb/s和100 Kb/s,所以不同速率時的4個周期的時間也不一樣,而且傳輸數據時每一位都有半個位周期是時鐘周期,因此需列出不同速率和周期對應的時長。本設計的時鐘選取為800 kHz,表2為此時鐘下的計數值。

從表2中可以看出,在100 Kb/s速率下4個位周期的計數值為32,而12.5 Kb/s時為256,所以無論任何速率當計數值為32時可認為是當前傳輸結束。但是,12.5 Kb/s速率時的半個位周期的計數值也為32,會出現錯誤。所以,選擇33為傳輸結束的計數值。

評論