用于移動寬帶基礎設施的新一代無線電數字前端解決

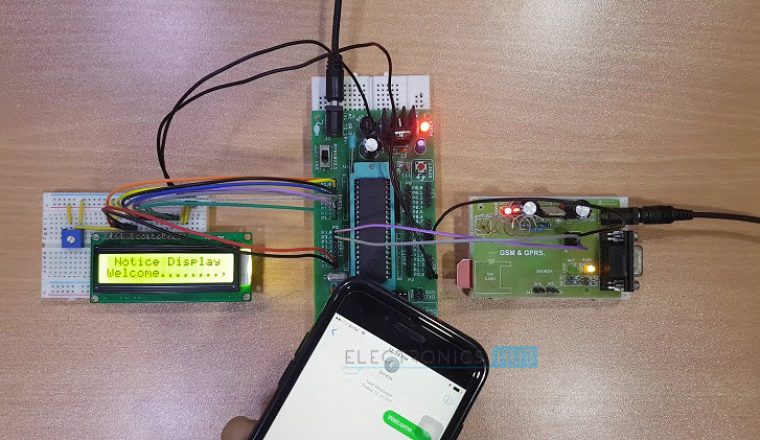

圖2說明了綜合使用ASSP、FPGA和微處理器構建的2x2的無線電設備。

ASSP一般適應市場需求的速度較慢,這在它們缺乏任何像CPRI或JESD204這樣的串行接口技術可以看出。這就需要一個輔助器件,比如內置有串行解串器的FPGA或使用外部串行解串器的低成本FPGA來完善設計。但這種設置需要大量的組件,從而導致PCB占位面積大,電源高度復雜,總功耗和成本都很高。

圖3所示的Zynq EPP采用雙ARM® Cortex™-A9處理器內核(每個內核的整數運算性能高達2000MIPS)和一個雙精度浮點單元。處理器子系統包含存儲器控制器、千兆位以太網、UART和SPI/I²C等專用通信外設。緊鄰處理器子系統的是高性能可編程邏輯,其內含500MHz DSP模塊、12.5Gbps串行解串器和大量的內部RAM。多條低時延、高帶寬總線用于連接處理器子系統和可編程邏輯,同時共享存儲器接口可保證避免發生性能瓶頸。

圖4所示的是設備制造商如何利用Zynq實現當今遠程無線電裝置中的全部功能。

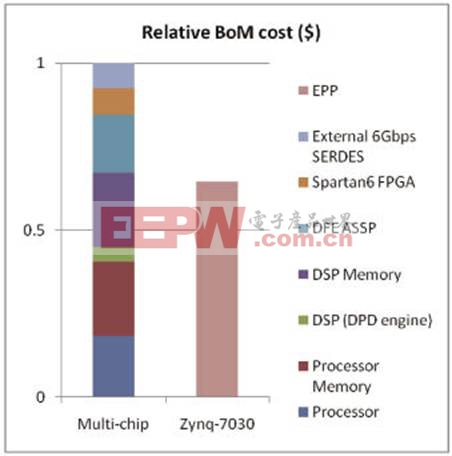

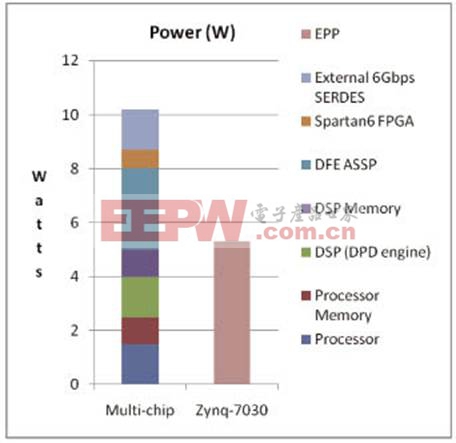

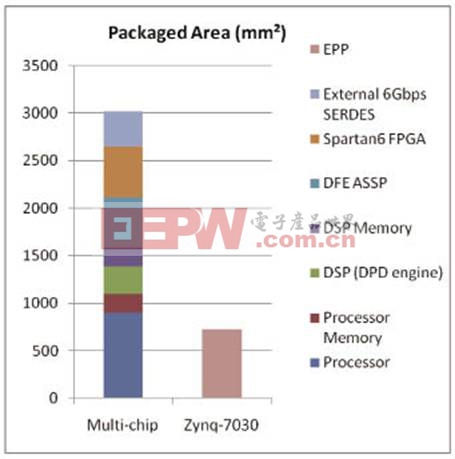

從圖5和圖6可以看出與現成的ASSP相比,這種架構能夠實現明顯的成本和功耗節約。這個示例假定信號帶寬為20MHz,有兩個發送和兩個接收路徑。Zynq還能夠支持更高的帶寬和更多數量的天線。

在2x2 20MHz LTE示例中,Zynq解決方案將功耗降低了高達50%,總材料成本相對等效ASSP設計降低了 35%~40%。另外,圖7還顯示,由于較圖2元組件數量減少,在提供圖4中相同的功能時,封裝面積可縮減達66%。

圖5 使用Zynq相對降低材料清單(BOM)成本

圖6 使用Zynq降低耗電

圖7 使用Zynq縮減封裝面積

使用Zynq還可以降低電源的復雜性和成本,同時提高無線電單元的可靠性。可靠性的提高能夠減少對市場退貨相關的后期執行費用的影響,還能夠實現更高的網絡可靠性。另外降低功耗還能夠減少散熱,從而可以使用尺寸更小、重量更輕的散熱器和機械結構。最后,Zynq解決方案能夠結合軟硬件靈活性,在設計后期才確定無線電單元的規范。這樣可以縮短產品上市時間,降低風險,在設備出貨后很長時間內還能支持新功能。本文引用地址:http://cqxgywz.com/article/185755.htm

評論