關于不同類型的時鐘討論

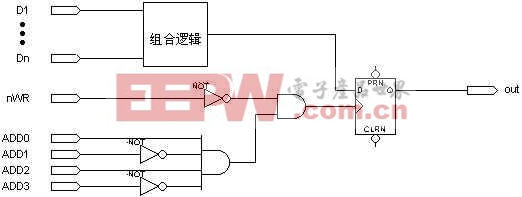

圖2 “與”門門控時鐘

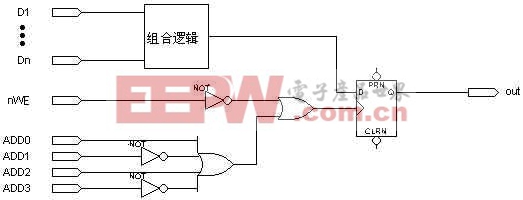

圖3 “或”門門控時鐘

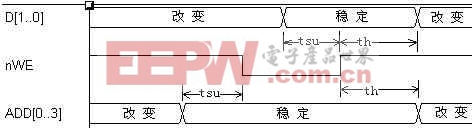

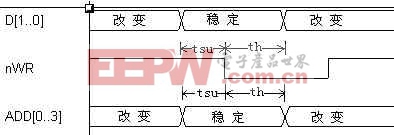

圖2和圖3 的波形圖顯示出有關的建立時間和保持時間的要求。這兩個設計項目的地址線必須在時鐘保持有效的整個期間內保持穩定(nWR和nWE是低電平有效)。如果地址線在規定的時間內未保持穩定,則在時鐘上會出現毛刺,造成觸發器發生錯誤的狀態變化。另一方面,數據引腳D[1..n]只要求在nWR和nWE的有效邊沿處滿足標準的建立和保持時間的規定。

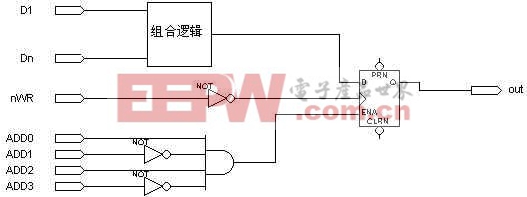

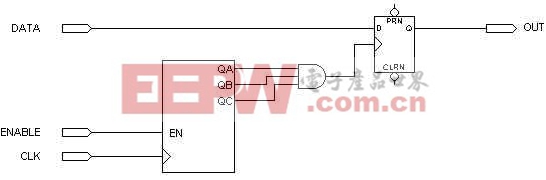

我們往往可以將門控時鐘轉換成全局時鐘以改善設計項目的可靠性。圖4 示出如何用全局時鐘重新設計 圖2 的電路。地址線在控制D觸發器的使能輸入,許多PLD設計軟件,如MAX PLUSII軟件都提供這種帶使能端的D觸發器。當ENA為高電平時,D輸入端的值被鐘控到觸發器中:當ENA為低電平時,維持現在的狀態。

圖4 “與”門門控時鐘轉化成全局時鐘

圖4 中重新設計的電路的定時波形表明地址線不需要在nWR有效的整個期間內保持穩定;而只要求它們和數據引腳一樣符合同樣的建立和保持時間,這樣對地址線的要求就少很多。

圖5給出一個不可靠的門控時鐘的例子。3位同步加法計數器的RCO輸出用來鐘控觸發器。然而,計數器給出的多個輸入起到時鐘的作用,這違反了可靠門控時鐘所需的條件之一。在產生RCO信號的觸發器中,沒有一個能考慮為實際的時鐘線,這是因為所有觸發器在幾乎相同的時刻發生翻轉。而我們并不能保證在PLD/FPGA內部QA,QB,QC到D觸發器的布線長短一致,因此,如圖5 的時間波形所示,在器從3計到4時,RCO線上會出現毛刺(假設QC到D觸發器的路徑較短,即QC的輸出先翻轉)。

圖5 不可靠的門控時鐘

(定時波形示出在計數器從3到4改變時,RCO信號如何出現毛刺的)

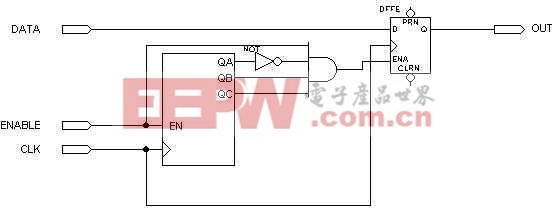

圖6 給出一種可靠的全局鐘控的電路,它是圖5不可靠計數器電路的改進,RCO控制D觸發器的使能輸入。這個改進不需要增加PLD的邏輯單元。

圖6 不可靠的門控時鐘轉換為全局時鐘

(這個電路等效于圖5電路,但卻可靠的多)

評論