一種用VHDL設計實現的有線電視機頂盒信源發生

1 VHDL的特點

VHDL是一種面向設計的、多層次、多領域且得一致認同的、標準的硬件描述語言。它主要有如下特點:

能形式化地抽象表示電路的結構和行為,降低了硬件電路設計的難度。

采用自上到下(Top-Down)的設計方法,支持邏輯設計中層次與領域的描述;它支持三個層次的描述:行為描述、RTL方式描述、門級描述(邏輯綜合)。

可進行系統的早期仿真以保證設計的正確性。

主要設計文件是VHDL語言編寫的源程序,便于文檔管理。

硬件描述與實現工藝無關。

由于VHDL語言已作為一種IEEE的工業標準,因而其語言標準、規范、語法比較嚴格,易于共享和復用。而且,VHDL設計技術齊全、方法靈活、支持廣泛。目前大多數EDA工具幾乎在不同程度上都支持VHDL語言。

2 CPLD外部引腳說明

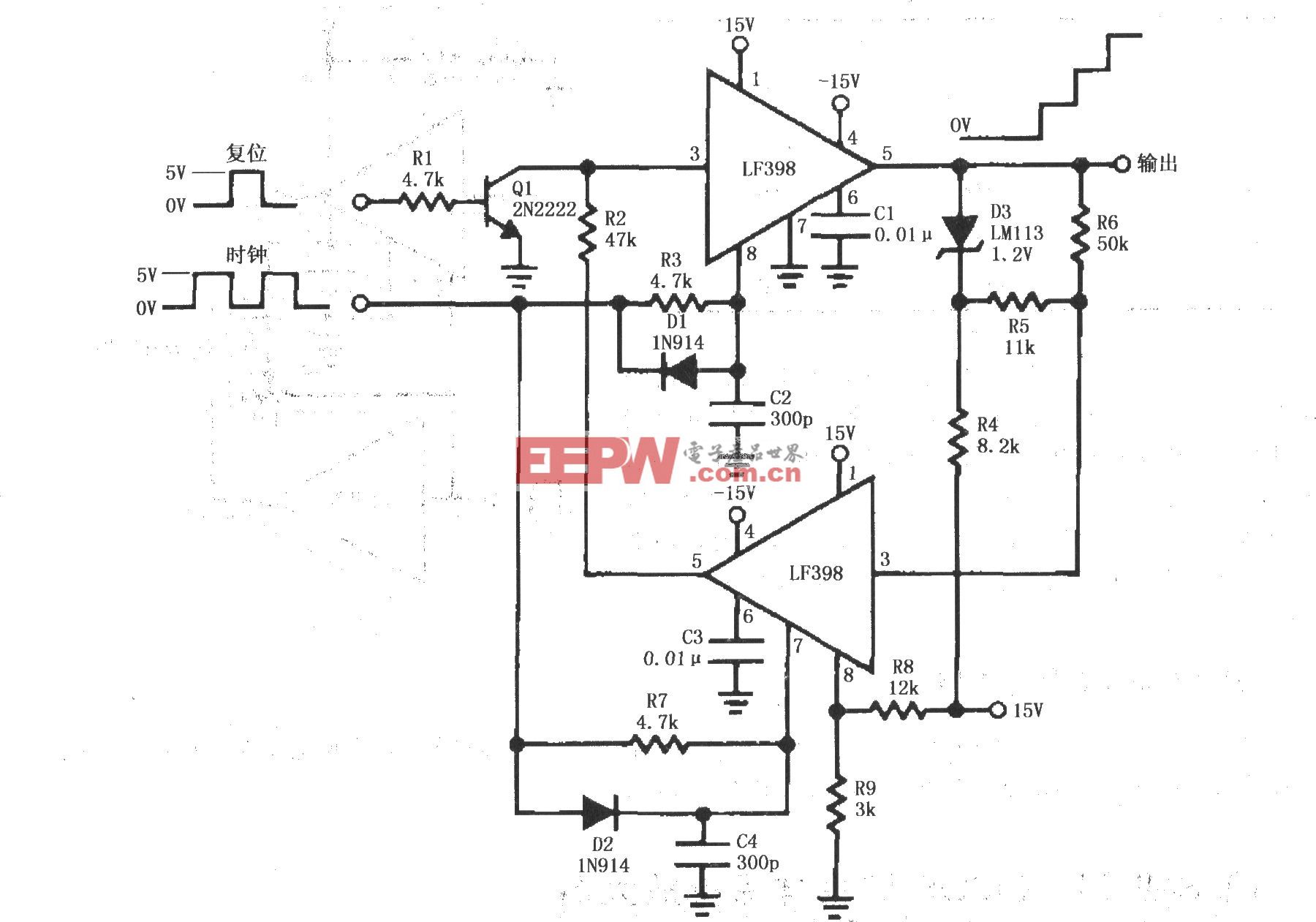

該方案中所用的芯片是Xilinx公司的CPLD 9500系列芯片,其類型為XC95108-7 PC84。這種芯片共有84個外部引腳,其中5個引腳接地,6個引腳接電源,4個引腳用于JTAG,剩下的引腳為I/O引腳。根據EISA總線的信號特征和信源的要求,該芯片所使用的外部引腳為如圖1所示。

圖1中輸入信號:

DATA_IN 15~0 輸入的數據信號

ADDRESS 15~0 輸入的地址信號

RESET 復位信號

AEN 地址允許信號

CLK 輸入時鐘信號

IOW I/O寫信號

輸出信號:

IO_CS 16位I/O片選信號

DATA_OUT 7~0 輸出的數據信號

DEN 輸出數據使能信號

DCLK 輸出數據時鐘信號

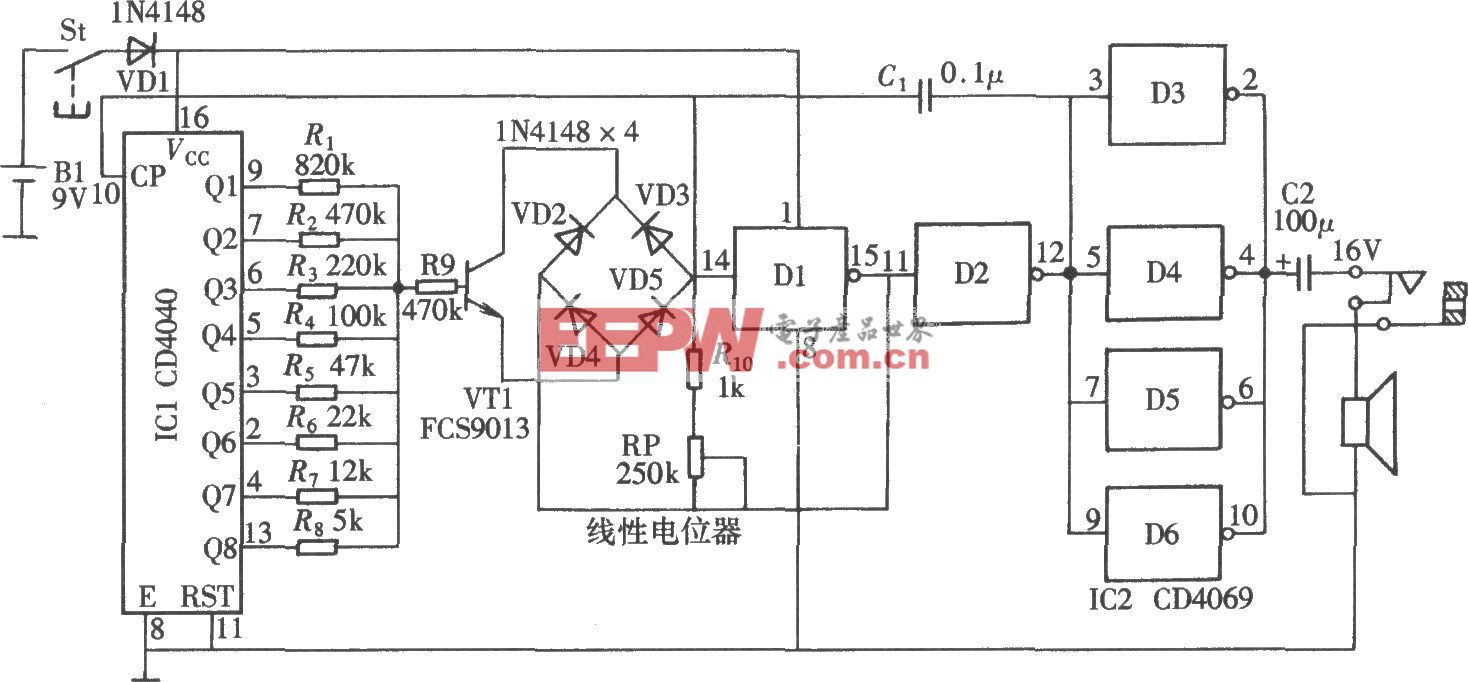

3 系統整體設計

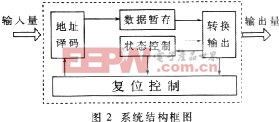

系統啟動后,主機向I/O口發出地址信號。AEN為低電平時,系統進行地址譯碼。譯碼成功后,產生一使能信號ENABLE打開數據暫存單元。數據到來后,數據暫存單元將總線上的16位并行數據鎖存在暫存器中,同時產生一允許信號PERMIT,允許進行數據格式轉換。接下來系統根據當前所處的狀態進行選擇輸出,完成格式的轉換,并產生相應的輸出數據使能信號DEN和輸出數據時鐘信號DCLK。整個過程結束后,將各信號復位,開始新的轉換周期。因此,整個系統應包括五個邏輯部分:地址譯碼、數據暫存、狀態控制、復位控制、轉換輸出。

3.1 系統的整體框圖

系統的整體框圖如圖2所示。

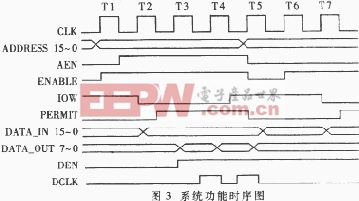

3.2 系統的工作時序

轉換過程的時序如圖3所示。

評論