基于HyperLynx的高速PECL交流耦合時鐘

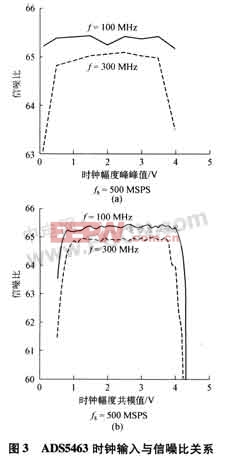

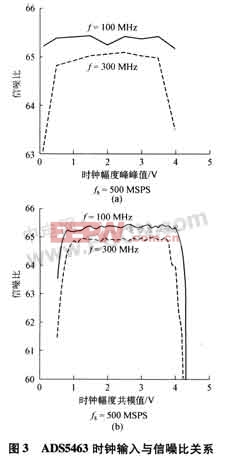

ADS5463的時鐘輸入特性如圖3所示。

|

|

3電路仿真

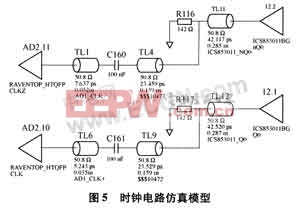

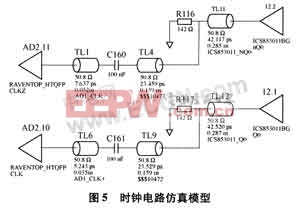

下面打開HyperLynx,將上述電路導入其中的LineSim工具下,該工具是HyperLynx的一個子工具,主要用來進行傳輸線的拓撲結構的仿真,可以對不同端接方式下的信號完整性進行分析。LineSim中的傳輸線模型構筑如圖5所示。

|

ADS5463的時鐘輸入特性如圖3所示。

|

|

3電路仿真

下面打開HyperLynx,將上述電路導入其中的LineSim工具下,該工具是HyperLynx的一個子工具,主要用來進行傳輸線的拓撲結構的仿真,可以對不同端接方式下的信號完整性進行分析。LineSim中的傳輸線模型構筑如圖5所示。

|

評論