一種高速低壓用增益增強型運算跨導放大器設計

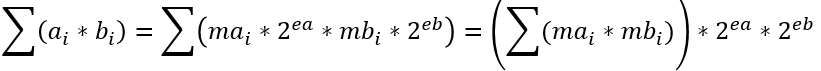

按照12位100MHz采樣頻率流水線A/D轉換器的采樣保持電路的指標來設計這個運算放大器。對動態誤差和靜態誤差所各自需要的增益和單位增益帶寬進行了折衷,將0.002%分配給靜態誤差,余下的0.008%給動態誤差。電路采用中芯國際(SMIC)0.18 μm混合信號CMOS工藝設計,1.8V電壓供電。具體設計指標為:開環增益:102dB:建立時間:4.3ns;精度:0.01%;單位增益帶寬:1.27GHz。頻率響應的曲線如圖4所示。本文引用地址:http://cqxgywz.com/article/188745.htm

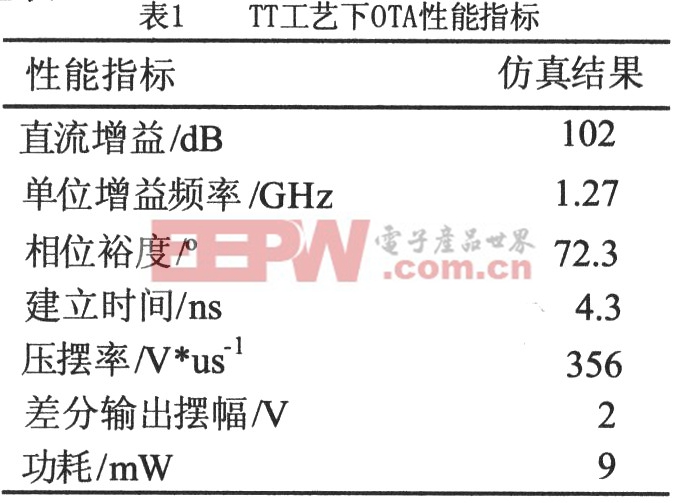

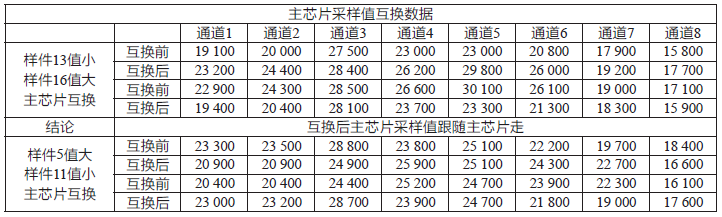

對運算放大器一些重要的性能參數在TT下仿真,結果的歸納見表1。

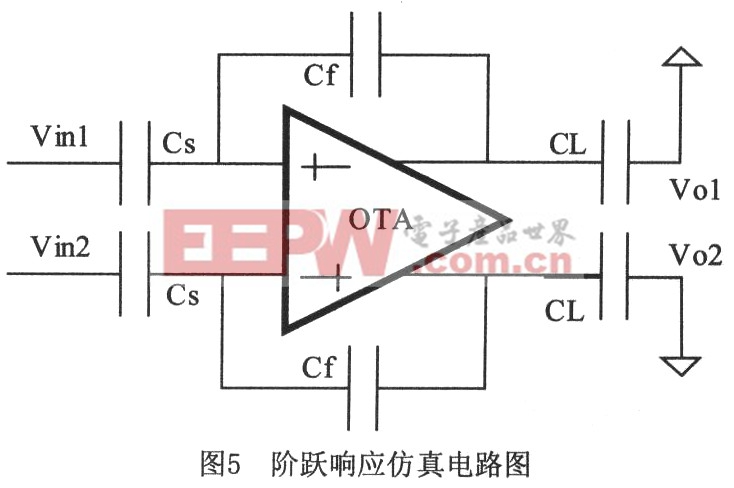

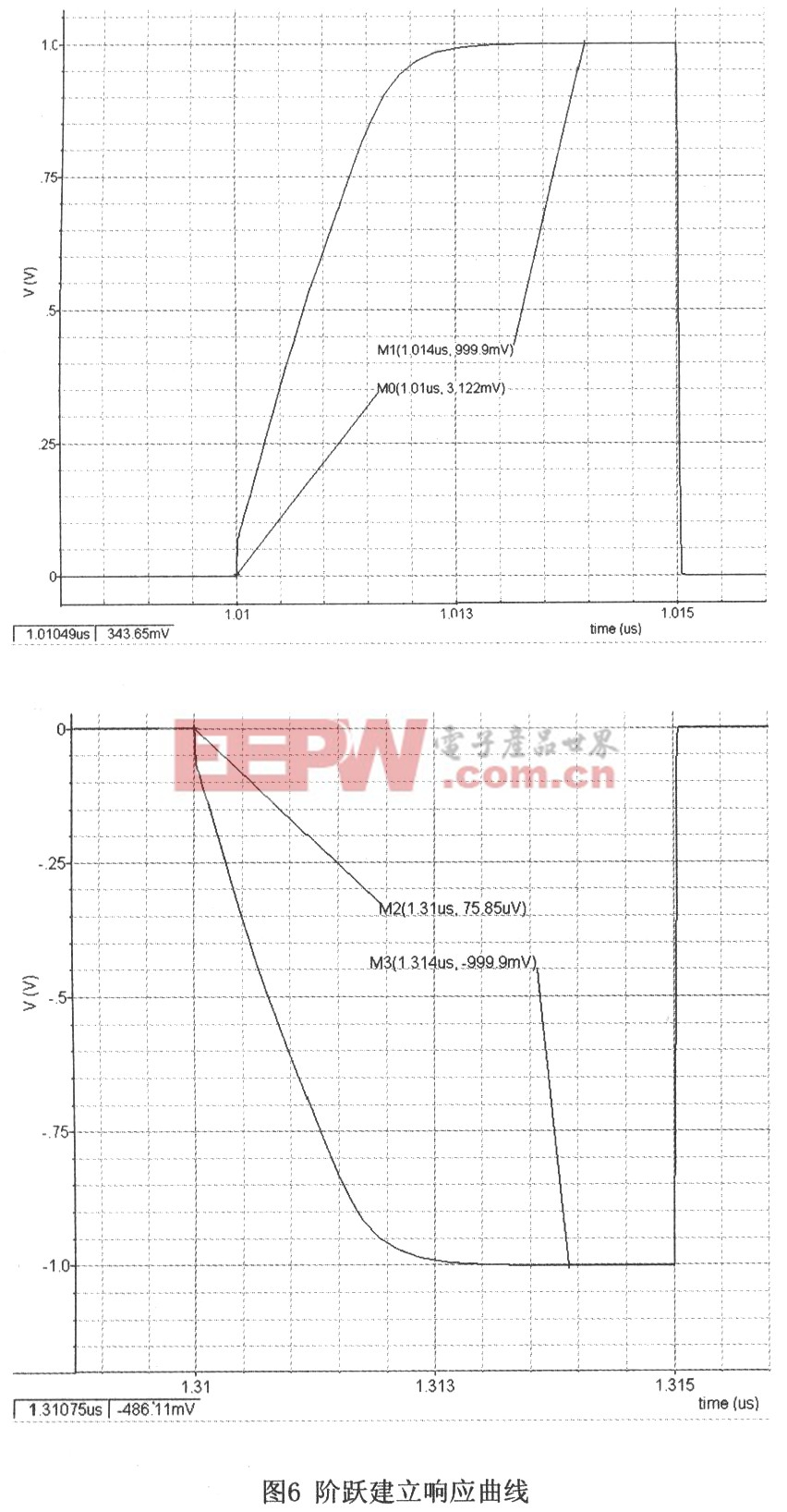

對階躍輸入響應的仿真在如圖5所示的閉環中進行。從運算放大器的輸入端引入一個±1V的大階躍信號,對應的建立時間曲線如圖6所示,表明所設計的電路能夠在4.3ns內達到終態0.01%的精度。

3 結論

本文提出了一種可用于增益增強運放高速設計的優化方法,并采用SMIC 0.18 μm混合信號CMOS工藝設計,實現了一個單級全差分增益增強的折疊共源共柵運算放大器。詳細分析并克服了零極點對可能引起的慢動態性能。仿真結果表明,此運算放大器能夠滿足高性能流水線A/D轉換器設計的要求。

評論