基于CPLD技術的PC104總線多功能擴展卡設計

多功能擴展卡的CPLD內部硬件設計包括:地址分配及譯碼電路、A/D模塊控制電路、

D/A模塊控制電路、開關量輸入/輸出模塊控制電路和正交解碼模塊控制電路。

2.2.1 地址分配及譯碼電路

地址分配及譯碼電路包括基地址發生電路和地址譯碼電路。在與嵌入式主板組成系統時,相對于嵌入式主板而言,多功能擴展卡是一個外圍設備,因此,首先要為該卡設置一個與系統內的其他外圍設備不相沖突的基地址,這由擴展卡的基地址設置開關及CPLD內部地址分配及譯碼電路完成。地址分配及譯碼電路由數值比較器74688、譯碼器74154等構成,

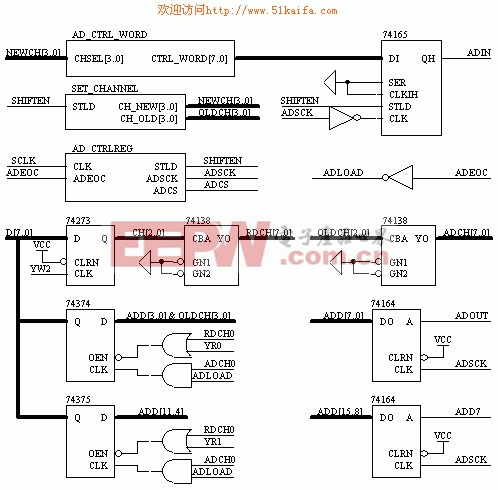

2.2.2 A/D模塊控制電路

A/D模塊控制電路的控制邏輯由兩部分組成:其一是實現嵌入式主板通過總線訪問各模擬通道的A/D轉換結果,由模擬通道選擇寄存器(74273)、轉換數據寄存器(74374)等構成;其二是提供A/D芯片的接口時序,實現A/D芯片八個通道的自動采樣和轉換,由串/并數據轉換邏輯(74164)、并/串數據轉換邏輯(74165)、通道掃描控制邏輯(AD_CTRL_WORD)、A/D控制時序邏輯(AD_CTRLREG)等構成。A/D模塊控制電路的電路設計如圖3所示(轉換數據寄存器只介紹一路)。本文引用地址:http://cqxgywz.com/article/188817.htm

圖3 多功能擴展卡A/D模塊控制電路

2.2.3 D/A模塊控制電路

D/A模塊控制電路由74373 IP軟核及相應控制邏輯構成,功能是同時刷新D/A芯片的輸入值。D/A控制模塊電路采用兩級鎖存電路刷新D/A芯片的輸入值,先置高4位字節數據,再置低8位字節數據,置低字節數據的同時使能D/A芯片的片選信號(/CS)、寫信號(/WE),然后置數據鎖存信號(/LDAC),刷新D/A的輸出。

2.2.4開關量輸入/輸出模塊控制電路

開關量輸入模塊控制電路由兩片74244 IP軟核及相應地址信號構成,開關量輸出模塊控制電路由兩片74273 IP軟核及相應地址信號構成。功能是實現嵌入式主板通過總線直接訪問各路開關量。

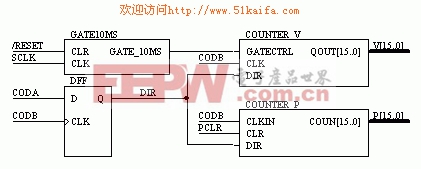

2.2.5 正交解碼模塊控制電路

正交解碼模塊控制電路是針對正交光電編碼器設計的,由方向識別邏輯(DFF)、閘門時間定時器(GATE10MS)、異步清零位置可逆計數器(COUNTER_P)、異步清零速度可逆計數器(COUNTER_V)等構成,可用于測量電機輸出軸的轉動方向、位置、速度等運動信息。電路設計如圖4所示。

圖4 多功能擴展卡正交解碼模塊控制電路

3 結論

該多功能擴展卡已經成功地應用到國家體育總局奧運科技攻關項目“帆板搖帆訓練測試系統研究”中,成功地完成了對交流伺服電機式阻力源的控制。訪問協議與臺灣研華PC工控機ISA總線板卡兼容,可獲得組態軟件編程支持。采用了復雜可編程邏輯器件(CPLD)技術,大大提高了系統的可靠性、靈活性。

伺服電機相關文章:伺服電機工作原理

評論