基于SOPC數據采集與控制系統的設計

2 硬件設計

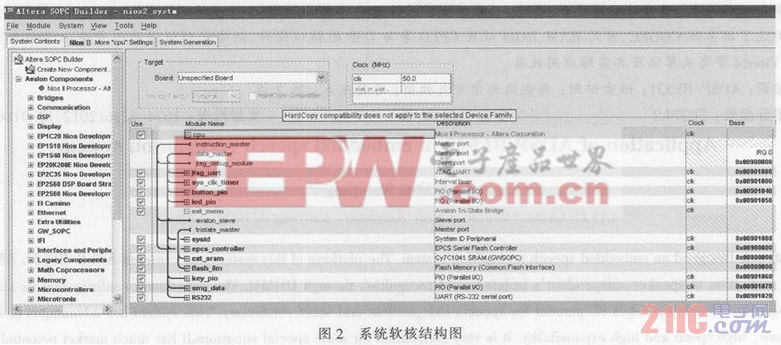

利用SOPC技術結合VHDL硬件描述語言,在FPGA芯片內部設計硬件控制部分;再加上外圍電路就構成了整個系統的硬件電路。FPGA內部各模塊利用Altera公司提供的Quartus II開發軟件和其中集成的SOPC Builder系統開發工具來設計。SOPC Builder支持Nios II CPU的配置,并支持設計者在其提供的IP庫中,根據系統設計需要選擇相應的接口模塊,加入到NiosII系統中,將這些設計在Quartus II中編譯并生成sof格式文件后,下載到FPGA芯片中就形成了SOPC的嵌入式系統硬件平臺。

2.1 NiosII軟核處理器

本設計選擇的處理器是Altera公司推出的第二代嵌入式NiosII軟核處理器。Nios II處理器系列是一種面向用戶的,可以靈活定制的通用RISC(精簡指令集架構)嵌入式CPU。Nios以軟核的方式提供給用戶,并專為在Altera的FPGA上實現作了優化,用于SOPC(片上可編程系統)集成,最后在FPGA上實現。

它的外設可以靈活選擇或增刪,可以自定制用戶邏輯為外設,可以允許用戶定制自己的指令集,使用Nios加上外部的Flash、SRAM即可構成一個嵌入式處理器系統。構建的軟核處理器如圖2所示。本文引用地址:http://cqxgywz.com/article/193299.htm

2.2 串行通信接口

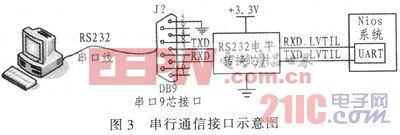

串行通信接口芯片選用MAX3232,由電平轉換芯片完成從LVTTL電平到RS232C電平的轉換,如圖3所示。

2.3 LED數碼管、發光二極管

8位數碼管顯示數據,通過接收的數據控制點亮相應的二極管。數碼管顯示譯碼在FPGA內部實現。發光二極管通過限流電阻直接接在FPGA的I/O口上。

2.4 Flash、SRAM存儲器、鍵盤

系統片外FLASH選用AM29LV065DU,片外SRAM選用UM611024A;作為運行Nios II的FLASH和SRAM。十個按鍵KEY0-KEY9直接與FPGA芯片的I/O口連接。

評論