基于CS5451A多路同步數據采集系統設計

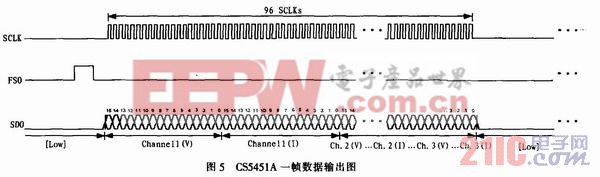

由于SCLK頻率很低,在用CPU的SPI控制器接收數據的時候,CPU接收一位的時間為4tXINe=1μs,如圖5所示,一幀數據為96位,接收一幀數據大約為96μs的時間,如果用CPU通過異步FIFO讀取數據,因為現在的控制器總線速度很快,假設讀一個字節數據需要100 ns,讀走一幀數據大約需要100 ns×12=1.2μs(由于MPC8313總線寬度為16位,不能一次讀取19位數據,所以在讀取FIFO中數據的時候,把通道號鎖存到一個暫存寄存器中,讀取采樣數據后再讀取通道號,所以讀取一幀數據需要12次)。只有原來的大約1/80的時間,提高了CPU的利用效率。

本文引用地址:http://cqxgywz.com/article/195006.htm

本文引用地址:http://cqxgywz.com/article/195006.htm

4 中斷服務子程序的設計

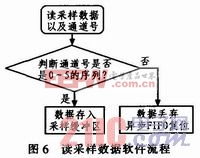

CPU讀采樣數據是在中斷服務子程序中設計的,在中斷程序中讀走采樣值數據,并判斷通道號是否對應。軟件流程如圖6所示。

5 結論

本文利用CS5451A設計一個通用的多路數據采集系統,利用XILINX SPARTAN3E系列FPGA芯片實現異步FIFO和采樣數據串并轉換模塊的設計,CPU不用直接用SPI控制器接收CS5451A芯片輸出的串行格式的數據,只需要把ADC輸出的串行數據通過串并轉換模塊存入FIFO緩沖區,并產生一個中斷信號,在CPU的中斷子程序中讀出采樣數據。該方案已經在低壓繼電保護裝置中得到了應用,通過試驗本系統的數據采集精度可以達到0.2級。調試中發現,在進行PCB設計時,要注意以下幾點:

1)模擬部分電路(差分輸入以及參考電源部分)和數字部分(XIN、FSO、SDO、SCLK信號)應完全分開在不同的區域里。

2)良好的去耦對抑制CS5451A產生的噪聲很重要,去耦電容一般為0.1 μF,且放到電源輸入引腳盡可能近的地方,以達到良好的去耦效果。

3)如果系統要求工作在-40~+85℃的溫度范圍內,要求采樣精度達到0.2級,必須使用外部高精度的參考電源。

評論