一種高速數據采集卡的設計與實現

3 數據采集卡電路設計

3.1 信號調理電路

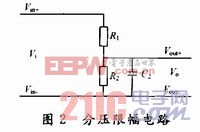

被測信號在進入A/D轉換器之前,都必須進行適當的處理,使之符合A/D轉換器的量程要求。對大信號需經過適當的衰減,而小信號則需要放大。本數據采集卡采用的A/D轉換器的輸入電壓峰峰值在0~1 V之間,而被測信號幅度都大于此值,所以信號在進入A/D轉換器之前需對其進行衰減處理。具體的分壓限幅電路如圖2所示。

3.2 A/D轉換與FIFO緩存電路

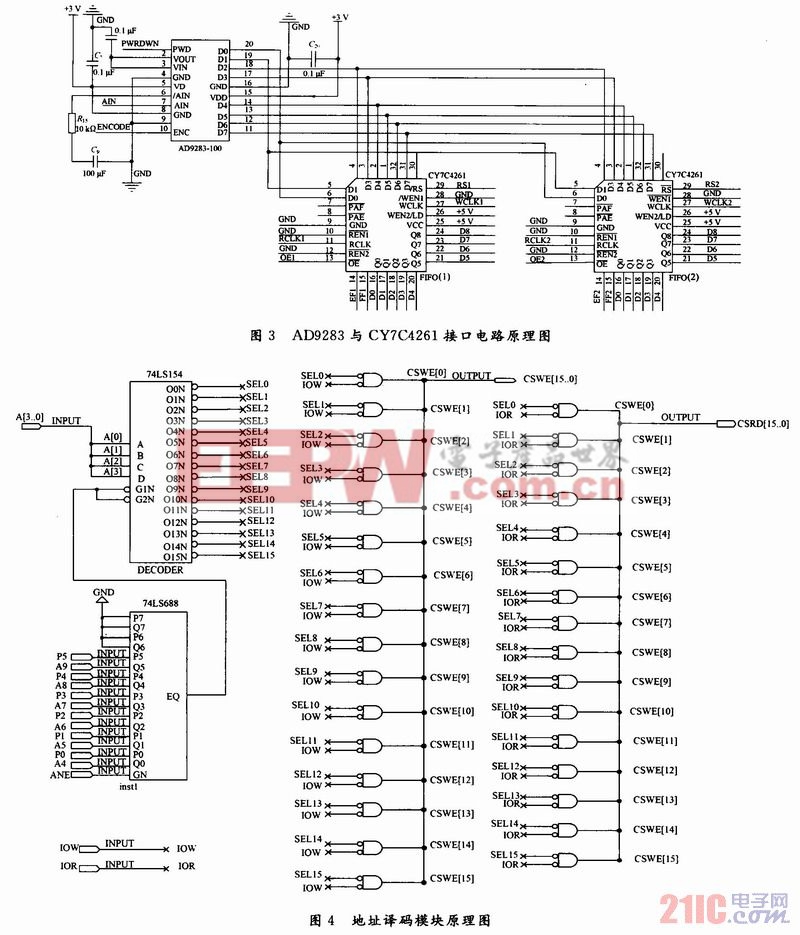

由于AD9283數據最大采集頻率為100 MHz,所以其最大數據存儲頻率至少應為100 MHz,而CY7C4261的最大存儲速率為100 MHz,能實現系統要求,系統中CY7C4261的寫時鐘與A/D轉換采用同一個時鐘進行控制。在測試過程中,有些待測信號周期較大,而本數據采集板的采樣頻率為100 MHz,為了在數據采集過程中不丟數據,需要連續采集大量數據。一片CY7C4261的存儲容量不夠,需要兩片輪流存儲。AD9283與CY7C4261的接口電路連接如圖3所示。

![]()

評論