1553B總線電纜網絡自動測試系統設計及研究

系統功能模塊

本系統的某些模塊可以直接選用現有模塊來實現,其中負責整個系統測試控制流程、數據分析、算法實現等工作的系統控制處理器,采用穩定性很好的工控機來實現;人機交互部分配合工控機選用液晶顯示器、鍵盤鼠標、打印機(實現測試結果報表的打印輸出),并結合測試界面軟件來實現;數據采集以及阻抗分析模塊采用具有編程接口的數字示波器來實現。

專用測試控制器

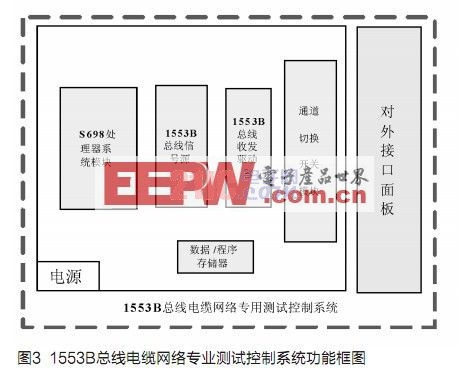

1553B總線電纜網絡專用測試控制器有兩大功能:作為電纜測試的信號源,產生測試用的標準1553B數字信號以及正弦波等激勵信號;完成測試過程中信號源輸入以及信號采集端的切換。專用測試控制器的功能框圖如圖3所示。

處理器系統模塊以及1553B總線信號源控制器模塊采用FPGA Cyclone III EP3C55F484 裝載S698 IP核+1553B IP核的形式來實現。珠海歐比特公司自主研發的S698 IP核是一款可裁減的基于AMBA總線架構的內核,片內帶有豐富的外設,具有很好的可靠性,已廣泛運用于航空航天領域。1553B IP核也是歐比特公司專門為航空、航天測控網絡中的設備開發的符合1553B協議的總線控制器模塊。該模塊內部實現了1553B總線協議處理器和總線數據收發器,可以完成總線控制器(BC)、遠程終端(RT)和總線監視器(BM)三種總線設備的功能。此處S698 IP核和1553B IP核均具有可剪裁性,根據測試系統的需要可以對其功能進行增加或減除。1553B軟核在FPGA內部實現全部MIL-STD-1553B總線協議的硬件解析,但1553B信號電平的邏輯轉換、驅動需要在外部通過收發驅動器實現。這里選用HOLT公司的1553B總線收發驅動器HI-1573進行設計。

綜合考慮系統的功能需求,程序存儲器采用了SST公司的8位FLASH,型號為39VF040(512×8bit),占用處理器的地址范圍為:0x0000000~0x0007ffff;數據存儲器采用了ISSI公司的16位SRAM,型號為IS61LV51216(512×16bit),占用處理器的地址范圍為:0x4000000~ 0x400fffff。

通道切換開關模塊主要完成激勵信號選擇性輸入到被測網絡以及選擇性采集被測網絡上的數據信號,因此用于選擇導通的開關必須具有導通電阻小、導通電容小等特性,從而極大減小開關對激勵信號或被采集信號的影響。綜合考慮各方面因素,選擇歐姆龍繼電器進行設計。

為了最大限度地兼容通用的1553B總線電纜網絡的接入測試,接口面板按照可接入32路1553B總線電纜網絡端點的需求來設計,同時每組接插件都是由1個孔型(DK-621-0940-4S)和1個針型(DK-621-0940-4P)插座組成,以兼容外部的針型(DK-621-0939-4P)和孔型插頭(DK-621-0939-4S)。

評論