時間交替ADC系統的實現

由(10)可知時間誤差是由于實際采樣時鐘發生了αk的偏差引起的,由此可以通過時域插值運算對實際采樣點t作一個t-αk的時間偏移以達到校正時間誤差的目的。

本文引用地址:http://cqxgywz.com/article/201609/304004.htm3 實驗結果

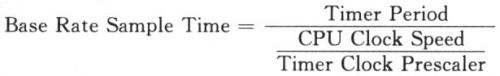

根據Cyclone III芯片手冊可以知道EP3C25Q240C8芯片中FIFO最大支持的時鐘頻率為238 MHz,同時校正算法中采樣頻率和信號頻率有fs=fo·N/m,因此實際設計中每個ADC采樣通道的采樣頻率為200MSPS,整個系統的采樣率最終達到400 MSPS。

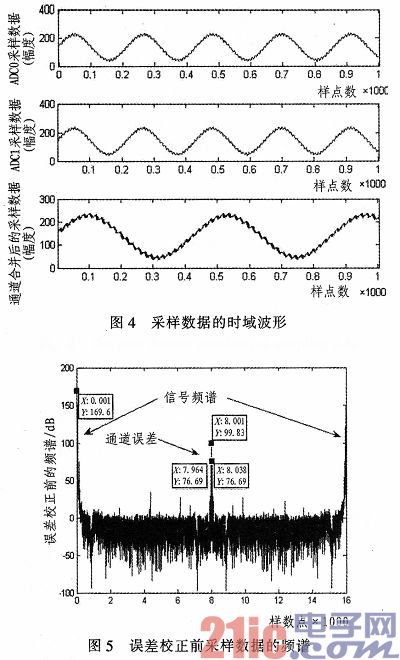

硬件電路設計完成后,在模擬輸入端接入幅值為300 mV,頻率為1 kHz,偏置和相位都為0的正弦信號作為模擬輸入信號,并將FPGA采集到的數據送到Matlab中進行數據分析和誤差校正,兩個通道每個通道采樣點數為8 000個點,下圖4中給出了兩路采樣數據以及兩通道采樣數據合并后的采樣數據(只取了其中100點采樣點的局部圖),可以看到,最后得到的系統采樣數據確實在相同的采樣點數內,采樣到的數據量為單通道采樣的數據量的兩倍,達到了提高采樣率的目的;同時,采樣數據確實存在著一定的誤差,這些誤差主要是通道間的失配誤差造成的。

通過Matlab軟件對采集到的數據進行頻譜分析和誤差校正,可以得到如下圖5和6所示的頻譜圖,圖5中所示的是對采集到的數據進行頻譜分析,兩個通道每個通道采樣點數為8 000個點,從圖中可以看到得到的3種通誤差點基本上是符合前面推斷的,同時通道誤差的幅度都比較大,嚴重影響了采樣系統的性能;圖6中所示的是經過誤差算法校正后采樣數據的頻譜圖,可以看到通道誤差基本上得到了校正,系統的信噪失真比和無雜散波動態范圍都得到了相應的提高。

4 結論

本文利用2片ADC采樣芯片及外圍電路實現了基于時間交替采樣技術的ADC系統,同時分析了這種時間交替采樣技術固有的3種通道誤差以及對ADC系統的影響;通過Matlab軟件分析采樣數據,觀察這種系統的頻譜特性,同時分析通道誤差的估算和校正方法,并對實際采樣系統系統進行了有效地誤差校正;實驗證明,通過時間交替采樣技術確實可以有效地提高采樣頻率,同時其通道誤差可以根據數學模型進行分析進而得到有效地校正,從而提高系統的性能。

評論