PCIe總線的基礎知識

1PERST#信號

該信號為全局復位信號,由處理器系統提供,處理器系統需要為PCIe插槽和PCIe設備提供該復位信號。PCIe設備使用該信號復位內部邏輯。當該信號有效時,PCIe設備將進行復位操作。PCIe總線定義了多種復位方式,其中Cold Reset和Warm Reset這兩種復位方式的實現與該信號有關,詳見第4.1.5節。

2REFCLK+和REFCLK-信號

在一個處理器系統中,可能含有許多PCIe設備,這些設備可以作為Add-In卡與PCIe插槽連接,也可以作為內置模塊,與處理器系統提供的PCIe鏈路直接相連,而不需要經過PCIe插槽。PCIe設備與PCIe插槽都具有REFCLK+和REFCLK-信號,其中PCIe插槽使用這組信號與處理器系統同步。

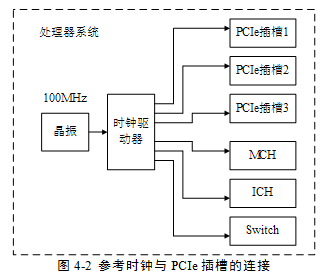

在一個處理器系統中,通常采用專用邏輯向PCIe插槽提供REFCLK+和REFCLK-信號,如圖4?2所示。其中100Mhz的時鐘源由晶振提供,并經過一個“一推多”的差分時鐘驅動器生成多個同相位的時鐘源,與PCIe插槽一一對應連接。

PCIe插槽需要使用參考時鐘,其頻率范圍為100MHz±300ppm。處理器系統需要為每一個PCIe插槽、MCH、ICH和Switch提供參考時鐘。而且要求在一個處理器系統中,時鐘驅動器產生的參考時鐘信號到每一個PCIe插槽(MCH、ICH和Swith)的距離差在15英寸之內。通常信號的傳播速度接近光速,約為6英寸/ns,由此可見,不同PCIe插槽間REFCLK+和REFCLK-信號的傳送延時差約為2.5ns。

當PCIe設備作為Add-In卡連接在PCIe插槽時,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信號,也可以使用獨立的參考時鐘,只要這個參考時鐘在100MHz±300ppm范圍內即可。內置的PCIe設備與Add-In卡在處理REFCLK+和REFCLK-信號時使用的方法類似,但是PCIe設備可以使用獨立的參考時鐘,而不使用REFCLK+和REFCLK-信號。

在PCIe設備配置空間的Link Control Register中,含有一個“Common Clock Configuration”位。當該位為1時,表示該設備與PCIe鏈路的對端設備使用“同相位”的參考時鐘;如果為0,表示該設備與PCIe鏈路的對端設備使用的參考時鐘是異步的。

在PCIe設備中,“Common Clock Configuration”位的缺省值為0,此時PCIe設備使用的參考時鐘與對端設備沒有任何聯系,PCIe鏈路兩端設備使用的參考時鐘可以異步設置。這個異步時鐘設置方法對于使用PCIe鏈路進行遠程連接時尤為重要。

在一個處理器系統中,如果使用PCIe鏈路進行機箱到機箱間的互連,因為參考時鐘可以異步設置,機箱到機箱之間進行數據傳送時僅需要差分信號線即可,而不需要參考時鐘,從而極大降低了連接難度。

3WAKE#信號

當PCIe設備進入休眠狀態,主電源已經停止供電時,PCIe設備使用該信號向處理器系統提交喚醒請求,使處理器系統重新為該PCIe設備提供主電源Vcc。在PCIe總線中,WAKE#信號是可選的,因此使用WAKE#信號喚醒PCIe設備的機制也是可選的。值得注意的是產生該信號的硬件邏輯必須使用輔助電源Vaux供電。

WAKE#是一個Open Drain信號,一個處理器的所有PCIe設備可以將WAKE#信號進行線與后,統一發送給處理器系統的電源控制器。當某個PCIe設備需要被喚醒時,該設備首先置WAKE#信號有效,然后在經過一段延時之后,處理器系統開始為該設備提供主電源Vcc,并使用PERST#信號對該設備進行復位操作。此時WAKE#信號需要始終保持為低,當主電源Vcc上電完成之后,PERST#信號也將置為無效并結束復位,WAKE#信號也將隨之置為無效,結束整個喚醒過程。

PCIe設備除了可以使用WAKE#信號實現喚醒功能外,還可以使用Beacon信號實現喚醒功能。與WAKE#信號實現喚醒功能不同,Beacon使用In-band信號,即差分信號D+和D-實現喚醒功能。Beacon信號DC平衡,由一組通過D+和D-信號生成的脈沖信號組成。這些脈沖信號寬度的最小值為2ns,最大值為16us。當PCIe設備準備退出L2狀態(該狀態為PCIe設備使用的一種低功耗狀態)時,可以使用Beacon信號,提交喚醒請求。

4SMCLK和SMDAT信號

SMCLK和SMDAT信號與x86處理器的SMBus(System Mangement Bus)相關。SMBus于1995年由Intel提出,SMBus由SMCLK和SMDAT信號組成。SMBus源于I2C總線,但是與I2C總線存在一些差異。

SMBus的最高總線頻率為100KHz,而I2C總線可以支持400KHz和2MHz的總線頻率。此外SMBus上的從設備具有超時功能,當從設備發現主設備發出的時鐘信號保持低電平超過35ms時,將引發從設備的超時復位。在正常情況下,SMBus的主設備使用的總線頻率最低為10KHz,以避免從設備在正常使用過程中出現超時。

在SMbus中,如果主設備需要復位從設備時,可以使用這種超時機制。而I2C總線只能使用硬件信號才能實現這種復位操作,在I2C總線中,如果從設備出現錯誤時,單純通過主設備是無法復位從設備的。

SMBus還支持Alert Response機制。當從設備產生一個中斷時,并不會立即清除該中斷,直到主設備向0b0001100地址發出命令。

上文所述的SMBus和I2C總線的區別還是局限于物理層和鏈路層上,實際上SMBus還含有網絡層。SMBus還在網絡層上定義了11種總線協議,用來實現報文傳遞。

SMBus在x86處理器系統中得到了大規模普及,其主要作用是管理處理器系統的外部設備,并收集外設的運行信息,特別是一些與智能電源管理相關的信息。PCI和PCIe插槽也為SMBus預留了接口,以便于PCI/PCIe設備與處理器系統進行交互。

在Linux系統中,SMBus得到了廣泛的應用,ACPI也為SMBus定義了一系列命令,用于智能電池、電池充電器與處理器系統之間的通信。在Windows操作系統中,有關外部設備的描述信息,也是通過SMBus獲得的。

5JTAG信號

JTAG(Joint Test Action Group)是一種國際標準測試協議,與IEEE 1149.1兼容,主要用于芯片內部測試。目前絕大多數器件都支持JTAG測試標準。JTAG信號由TRST#、TCK、TDI、TDO和TMS信號組成。其中TRST#為復位信號;TCK為時鐘信號;TDI和TDO分別與數據輸入和數據輸出對應;而TMS信號為模式選擇。

JTAG允許多個器件通過JTAG接口串聯在一起,并形成一個JTAG鏈。目前FPGA和EPLD可以借用JTAG接口實現在線編程ISP(In-System Programming)功能。處理器也可以使用JTAG接口進行系統級調試工作,如設置斷點、讀取內部寄存器和存儲器等一系列操作。除此之外JTAG接口也可用作“逆向工程”,分析一個產品的實現細節,因此在正式產品中,一般不保留JTAG接口。

6PRSNT1#和PRSNT2#信號

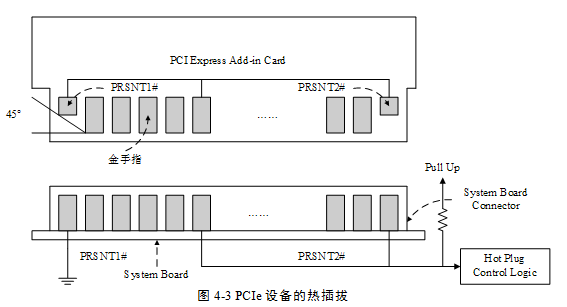

PRSNT1#和PRSNT2#信號與PCIe設備的熱插拔相關。在基于PCIe總線的Add-in卡中,PRSNT1#和PRSNT2#信號直接相連,而在處理器主板中,PRSNT1#信號接地,而PRSNT2#信號通過上拉電阻接為高。PCIe設備的熱插拔結構如圖4?3所示。

如上圖所示,當Add-In卡沒有插入時,處理器主板的PRSNT2#信號由上拉電阻接為高,而當Add-In卡插入時主板的PRSNT2#信號將與PRSNT1#信號通過Add-In卡連通,此時PRSNT2#信號為低。處理器主板的熱插拔控制邏輯將捕獲這個“低電平”,得知Add-In卡已經插入,從而觸發系統軟件進行相應地處理。

Add-In卡拔出的工作機制與插入類似。當Add-in卡連接在處理器主板時,處理器主板的PRSNT2#信號為低,當Add-In卡拔出后,處理器主板的PRSNT2#信號為高。處理器主板的熱插拔控制邏輯將捕獲這個“高電平”,得知Add-In卡已經被拔出,從而觸發系統軟件進行相應地處理。

不同的處理器系統處理PCIe設備熱拔插的過程并不相同,在一個實際的處理器系統中,熱拔插設備的實現也遠比圖4?3中的示例復雜得多。值得注意的是,在實現熱拔插功能時,Add-in Card需要使用“長短針”結構。

如圖4?3所示,PRSNT1#和PRSNT2#信號使用的金手指長度是其他信號的一半。因此當PCIe設備插入插槽時,PRSNT1#和PRSNT2#信號在其他金手指與PCIe插槽完全接觸,并經過一段延時后,才能與插槽完全接觸;當PCIe設備從PCIe插槽中拔出時,這兩個信號首先與PCIe插槽斷連,再經過一段延時后,其他信號才能與插槽斷連。系統軟件可以使用這段延時,進行一些熱拔插處理。

4.1.3PCIe總線的層次結構

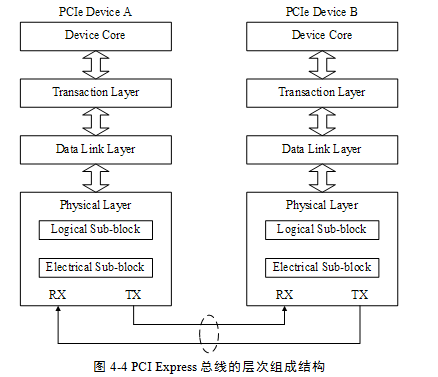

PCIe總線采用了串行連接方式,并使用數據包(Packet)進行數據傳輸,采用這種結構有效去除了在PCI總線中存在的一些邊帶信號,如INTx和PME#等信號。在PCIe總線中,數據報文在接收和發送過程中,需要通過多個層次,包括事務層、數據鏈路層和物理層。PCIe總線的層次結構如圖4?4所示。

PCIe總線的層次組成結構與網絡中的層次結構有類似之處,但是PCIe總線的各個層次都是使用硬件邏輯實現的。在PCIe體系結構中,數據報文首先在設備的核心層(Device Core)中產生,然后再經過該設備的事務層(Transaction Layer)、數據鏈路層(Data Link Layer)和物理層(Physical Layer),最終發送出去。而接收端的數據也需要通過物理層、數據鏈路和事務層,并最終到達Device Core。

評論