PCI總線互連之時序分析與仿真驗證

1. 信號完整性仿真的一個實例說明

PCB設計與仿真背景介紹:10Gb網絡交換基板(Basecard)。一些參考設計數據列舉如下:

a. 基板特點。雙ixp2800網絡處理器設計,可支持多口百兆電口與多口1Gb以太網業務及OC-192 10Gb業務數據端口等光口,64位/66MHz CPCI(Compact PCI)底板接口。

b. 網絡處理器(NPU)。Intel ixp2800主芯片,16個集成微引擎(實現超高速數據層并行處理能力),工作速率為1.4 GHz;一個XScale內核(核心管理器),工作速率為700MHz。

c. 集成高速內存控制器。工業標準RDRAM,工作速率為800/1,066MHz,峰值速率為2.1GBps,QDRII SRAM,工作速率為233MHz,每通道峰值速率為1.9GBps。

d. 集成媒介交換接口。2個單向16位的LVDS差分信號,工作速率為500MHz,SPI-4或CSIX協議。

2. PCI總線的仿真與驗證

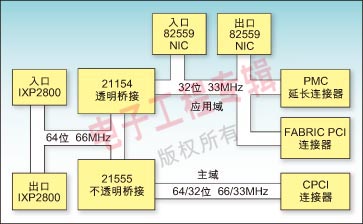

圖3描述了整板PCI設備之間的互連關系。如圖3所示,設備互連關系較復雜,如何保證正確的時序是設計成功與否的關鍵。

圖3:PCI設備互連關系圖

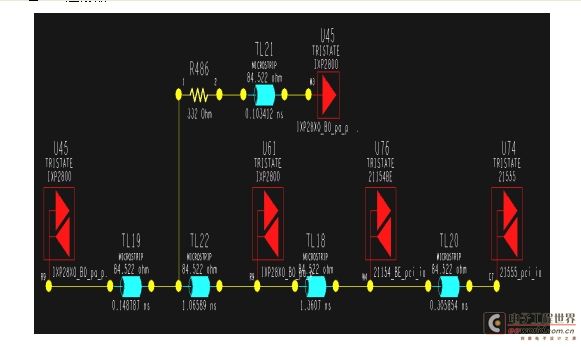

圖4給出了經提取的N_PCI_AD23(有IDSEL信號功能)的拓撲結構圖(Topology),表示主域(host domain)端的電路連接關系。

圖4:N_PCI_AD23信號拓撲結構圖

經過對仿真與驗證階段的仿真參數的調整、仿真的實施(仿真模型在布局階段已作建立),得到如下建立與保持時間(setup/hold)數據,見表1。

表1:PCI地址/數據復用總線的setup/hold時序表

由于為64位總線,本表僅列舉了部分總線信號數據,同時列舉了相關PCI規范(ver2.3)要求,以作對比并形成判斷的基準。本處省略公共時鐘(common-clock)總線時序的理論推導與數據分析,只作設計結果的數據分析與驗證。表1中的3ns/0ns的setup/hold數據來源于PCI局部總線規范REV2.3。

對設計提取的表示點對點的連接關系的N_PCI_REQ(總線請求與授權信號)時序表數據簡要摘錄如下:規范要求的setup/hold為5ns/0ns,實際范圍在5.824-7.292ns/3.443-5.426ns之間,由此數據可知,setup/hold較其它總線時序寬松很多。

經過對所有PCI總線相關信號的仿真數據的分析,包括主域與應用域(utility domain)端,可以得出結論,本環節設計合格,可以進行其它環節的仿真與驗證。

參考文獻

1.IXP2800 NPU DATASHEET,Intel Corporation.

2.STEPHEN H.HALL,GARRETT W.HALL,JAMES A.MCCALL.HIGN-SPEED DIGITAL SYSTEM DESIGN.

評論