SPI總線協議及SPI時序圖詳解

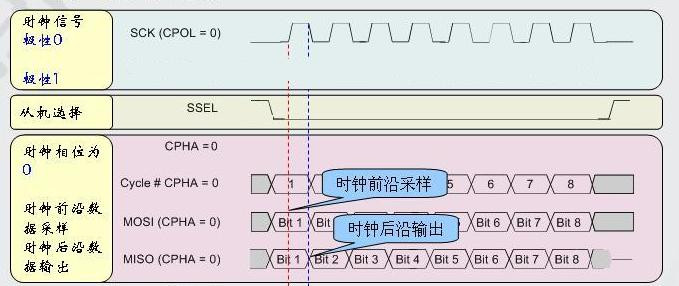

由于我使用的器件工作在模式0這種時序(CPOL=0,CPHA=0),所以將圖簡化為圖2,

只關注模式0的時序。

圖2

我們來關注SCK的第一個時鐘周期,在時鐘的前沿采樣數據(上升沿,第一個時鐘沿),

在時鐘的后沿輸出數據(下降沿,第二個時鐘沿)。首先來看主器件,主器件的輸出口(MOSI)輸出的數據bit1,

在時鐘的前沿被從器件采樣,那主器件是在何時刻輸出bit1的呢?bit1的輸出時刻實際上在SCK信號有效以前,

比 SCK的上升沿還要早半個時鐘周期。bit1的輸出時刻與SSEL信號沒有關系。再來看從器件,

主器件的輸入口MISO同樣是在時鐘的前沿采樣從器件輸出的bit1的,那從器件又是在何時刻輸出bit1的呢。

從器件是在SSEL信號有效后,立即輸出bit1,盡管此時SCK信號還沒有起效。關于上面的主器件

和從器件輸出bit1位的時刻,可以從圖3、4中得到驗證。

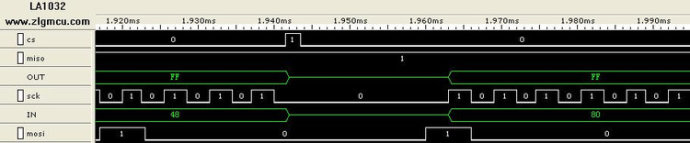

圖3

注意圖3中,CS信號有效后(低電平有效,注意CS下降沿后發生的情況),故意用延時程序

延時了一段時間,之后再向數據寄存器寫入了要發送的數據,來觀察主器件輸出bit1的情況(MOSI)。

可以看出,bit1(值為1)是在SCK信號有效之前的半個時鐘周期的時刻開始輸出的(與CS信號無關),

到了SCK的第一個時鐘周期的上升沿正好被從器件采樣。

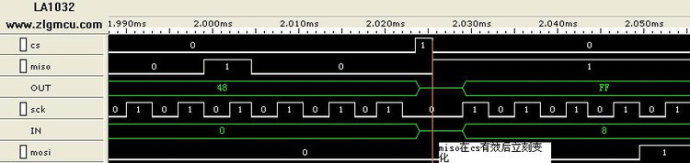

圖4

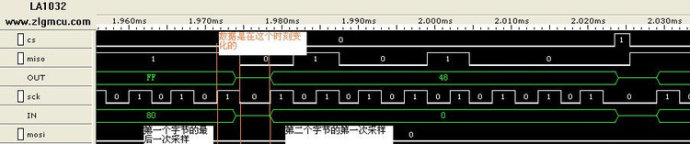

圖4中,注意看CS和MISO信號。我們可以看出,CS信號有效后,從器件立刻輸出了bit1(值為1)。通常我們進行的spi操作都是16位的。圖5記錄了第一個字節和第二個字節間的相互銜接的過程。

第一個字節的最后一位在SCK的上升沿被采樣,隨后的SCK下降沿,從器件就輸出了第二個字節的第一位。

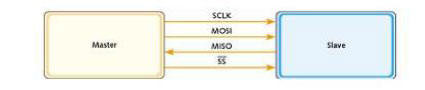

SPI總線協議介紹(接口定義,傳輸時序)

一、技術性能

SPI接口是Motorola 首先提出的全雙工三線同步串行外圍接口,采用主從模式(Master Slave)架構;支持多slave模式應用,一般僅支持單Master。

時鐘由Master控制,在時鐘移位脈沖下,數據按位傳輸,高位在前,低位在后(MSB first);SPI接口有2根單向數據線,為全雙工通信,目前應用中的數據速率可達幾Mbps的水平。

-------------------------------------------------------

二、接口定義

SPI接口共有4根信號線,分別是:設備選擇線、時鐘線、串行輸出數據線、串行輸入數據線。

(1)MOSI:主器件數據輸出,從器件數據輸入

(2)MISO:主器件數據輸入,從器件數據輸出

(3)SCLK :時鐘信號,由主器件產生

(4)/SS:從器件使能信號,由主器件控制

-------------------------------------------------------

三、內部結構

四、傳輸時序

SPI接口在內部硬件實際上是兩個簡單的移位寄存器,傳輸的數據為8位,在主器件產生的從器件使能信號和移位脈沖下,按位傳輸,高位在前,低位在后。如下圖所示,在SCLK的下降沿上數據改變,上升沿一位數據被存入移位寄存器。

SPI接口沒有指定的流控制,沒有應答機制確認是否接收到數據。

評論