基于SOPC的車輛總線控制器設計方案

3 SOPC片上系統MVB控制器設計

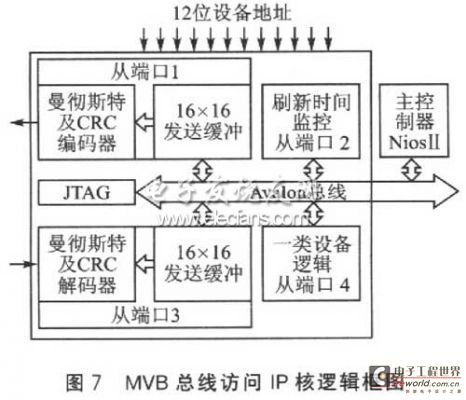

3.1 總線訪問IP核與NiosII的系統集成

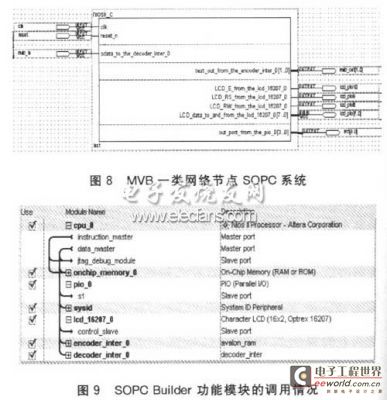

利用QuartersII的SOPC Builder工具,集成了1個32位NiosII軟核處理器、4 KB的片內RAM、MVB總線訪問IP核(包括編碼器和解碼器)以及LCD控制模塊,在Altera的CycloneII FPGA上構成了一個能實現MVB一類網絡節點功能的片上系統,如圖8所示。圖9為SOPCBuilder中各個功能模塊的凋用情況。

3.2 NiosII處理器上的軟件設計

基于上述SOPC系統,設計了一個基本的MVB節點,以實現過程數據傳輸。該節點將Oxl4地址設置為源端口。當主幀輪詢0x14地址時,本節點將此端口里的數據打包成從幀發送到總線上面,以刷新0x14地址的宿端口。

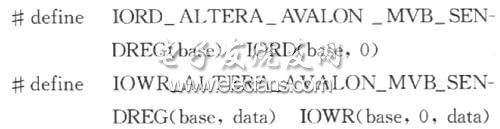

MVB模塊頭文件altera_avalon_mvb.h的設計,包括總線訪問IP核寄存器讀寫的宏定義。

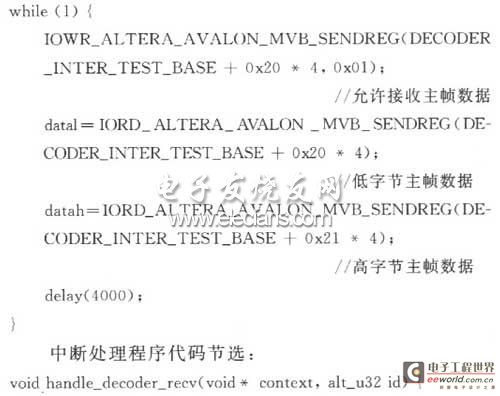

在主函數里置MVB總線接收允許位,循環等待接收MVB主控制器發過來的主幀。節點在接收到主幀之后,程序進入中斷處理程序。在巾斷程序里提取接收到的主幀里的端口地址,并與自身預設的端幾地址碼進行比較。如果地址碼相符,則節點將本端口的數據通過MVB發送器發到總線上,實現端口數據刷新操作。

主循環代碼節選:

4 仿真與實測波形

4.1 仿真波形

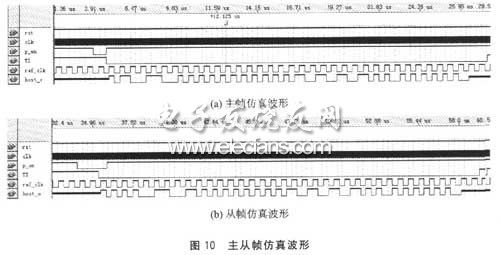

在本實驗中,對實驗室設計的MVB板卡進行了功能仿真和FPGA驗證.通過對過程數據的發送與接收驗證了所搭建的MVB系統。對MVB總線控制器發送過程的主從幀仿真結果如圖10所示。發送的主從幀數據都為0x0055,包含1個幀頭及8位CRC校驗數據。

4.2 實測波形

編好程序后,再編譯一遍QuartersII工程文件,將得到的.pof文什下載至FPGA內。上電后用示波器測輸出引腳,便可觀察到MVB從幀波形,實測波形如圖11所示。對照IEC-61375協議標準,可以判斷出該渡形為符合標準的正確波形,并且源端口節點上收到了正確的數據,從而證明該過程數據端口成功刷新。

結語

目前,MVB控制器實現了實驗室環境中過程變量的正確接收和發送。本總線訪問IP核實現的功能與MVBC相當,但是由于采用了先進的SOPC設計技術,其體系結構大大簡化,設計難度也大大降低,在通用性方面有了很大的提高。

評論