高速便攜式RS232/422信號模擬器設計

2. 3 FPGA核心控制電路模塊設計

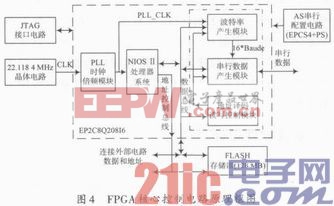

FPGA核心控制電路監控以上各電路模塊的工作狀態,隨時準備接收來自它們的數據和命令,并進行相應的控制。它包括了控制部分和串行數據生成部分,控制部分是在FPGA芯片內部嵌入Alter公司提供的NIOSⅡ的處理器IP軟核,利用QuartusⅡ軟件內部的SOPC工具生成FPGA內部的控制電路。串行數據生成部分利用VHDL硬件編程語言編制了波特率發生器和并串轉換模塊生成RS232/422串行信號數據。所有的控制電路都是通過軟件定制在一片FPGA芯片內,外圍電路比較簡單,除了正常的程序加載電路和程序存儲芯片,僅需要一片時鐘芯片即可。FPGA核心控制電路原理圖如圖4所示。

3 系統軟件設計

3.1 波特率和串行數據產生模塊設計

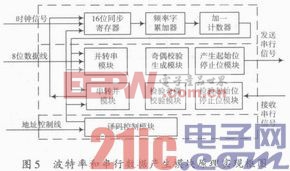

串行數據產生模塊負責生成符合格式設置要求的串行數據,如起始位,數據位,效驗位,停止位等。它主要是把控制器發送的并行數據轉換成串行數據,并根據控制器發送的效驗位,停止位等設置命令來設置數據的格式,以來自波特率產生模塊的16倍的波特率作為全局時鐘,生成要模擬的RS232/422信號數據。

波特率產生模塊根據控制器發送的命令數據來產生符合要求的波特率。在本系統中,要求產生24種標準和非標準的波特率,其中標準的波特率16種,非標準波特率8種,最高的波特率達到1 Mb/s,這樣利用常規的分頻器不能滿足要求。

依據DDS(直接數字頻率合成)的原理,結合積分分頻電路,設計了頻率字累加器,通過從NIOSⅡ控制器輸入的頻率字來控制累加器的累加步長,將累加器輸出的最高位作為輸出的時鐘信號的方法實現所需要的波特率時鐘,此時輸出的時鐘即可作為串行數據產生模塊的全局時鐘,也就是16倍的波特率。同時為了提高時鐘的精確度,降低誤碼率,在系統時鐘(這里采用的是22 11 8 4 MHz)進入分頻器以前,利用PLL倍頻電路提高時鐘的頻率。

波特率和串行數據產生模塊在FPGA內部的原理實現框圖如5圖所示。它的實現是采用VHDL硬件描述語言實現的,框圖中每個小的模塊代表VHDL語言編制的模塊程序。

3.2 NIOSⅡ控制器系統定制和內部程序設計

傳統的MCU,DSP或ARM等硬處理器或控制器,它們的功能和片內外設都是固化好的,用戶只能使用,而不能做任何改動。而NIOSⅡ處理器是FPGA芯片生成廠商Altera公司無償提供的軟IP核,可以通過QuanusⅡ軟件對它進行設置,隨時可以添加在片的ROM或RAM,并去掉不必要的外設,使得整個系統的搭建靈活,方便,簡潔。并且,在硬件系統的設計上,一片FPGA芯片內就可以完成整個的數字控制系統,使得硬件系統的設計非常的簡單可靠,性能也非常的穩定。

在本系統的設計中,NIOSⅡ處理器和傳統的MCU,DSP或ARM等硬處理器或控制器一樣,也可以用C語言編程實現需要的控制功能,也可以嵌入各種嵌入式操作系統,并進行調試等。編程的開發環境是專用的NIOS2-IDE集成開發環境。

評論