基于FPGA和多DSP的多總線并行處理器設計

2.2基于FPGA的多DSP系統接口電路設計

在本系統中,要求利用一個主處理器來控制3片DSP,完成主處理器與各DSP的控制及散據傳輸,為了提高傳輸速率,保證控制的靈活性、準確性,我們利用FPGA設計一種綜合實用的多DSP的接口電路。

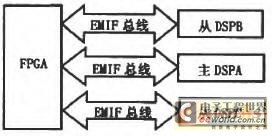

由于系統中包含3片DSP,設計時采用系統層次化,結構模塊化、數據傳輸高速化的設計思想,利用FPGA作為接口設計的部件,實現系統的接口電路原理如圖2所示。

圖2 FPGA與DSP通信框圖

系統層次化體現在控制結構之中,考慮到多片DSP的接口t控制與數據傳輸以層次化結構為主,以寄存器作為控制接口的物理層,每個DSP均有其自身的控制寄存器,以實現多個DSP的控制,以FIFO作為數據傳輸的物理層。在軟件設計中增加了控制的靈活性及數據傳輸的高速率。結構模塊化體現在DSP組的結構中,根據多塊DSP接口的特點,在系統結構設計中,將3片DSP用一十FPGA來完成物理層硬件接口電路,這樣使得系統結構清晰,模塊擴充靈活方便,又可節省費用。

2.3系統外部接口設計

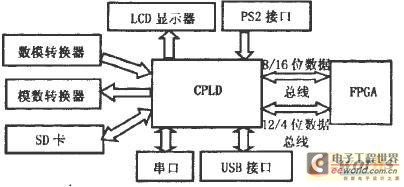

根據數據處理需求,系統設計了豐富的外圍接口電路,并通過FPGA擴展的CPLD來進行管理。如圖3所示.

圖3 系統功能框圖

2.4 ADC設計

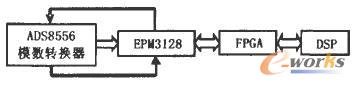

圖4為系統設計的.NDC硬件框圖.基于CPLD、FPGA和DSP的多通道同步數據采集系統主要由數據采集模塊、數據處理模塊以及散據接口模塊3部分構成。前端由傳感器輸入的模擬信號經信號調理模塊的整形放大后,輸入到A/D轉換模塊中,模擬量轉變為數字量,可編程邏輯器件(CPLD)控制A/D轉換器,按照設定的采樣率采集數據,將采集到的數據通過總線寫入FIFO,FIFO半滿時,發送一次半滿信號,FPGA接收到中斷后立即將一幀數據從FIFO中讀入到數據處理模塊,進行初步處理并通知相應的DSP對其進行調用,做進一步分析。

圖4 ADC硬件框圖

該系統的A/D轉換模塊選用TI公司的ADS8556型A/D轉換器,該件支持6通道信號差分輸入,有3組信號采集控制端,每組控制2路信號.16位精度,每通道的轉換速度高達450 kHz。支持高速并行數據輸出接口,數據輸出接口包括直接地址選擇模式、CYCLE模式、FIFO模式。

2.5 CPLD部分設計

CPLD控制部分:CPLD1控制ADS8556包括控制A/D轉換器的采樣率以及數據量化輸出模式等,同時控制CS信號可有效抑制噪聲;系統時鐘輸入為50 MHz,CPLD對其分頻產生20MHz時鐘以觸發A/D轉換器,同時產生200kH的采樣信號。

2.6數據幀格式設計

CPLD將A/D轉換后的數據不斷寫入FIFO,當2048字節數據寫入FIFO后,CPLD添加16位的幀標志及16位的幀計數,即數據格式為:被采集數據+幀標志+幀計數。

2.7系統時鐘設計

對于多DSP并行處理系統而言,系統各部分的時鐘配合以同步十分關鍵,不僅關系到系統的穩定運行,更重要的是系統內部的信息交換嚴重依賴于可靠地時鐘同步,特別是采用同步FIFO或RAM來傳遞數據的場合,同時可靠統一的系統時鐘也有利于數據傳輸效率的提升。

考慮到本系統容納了5片核心的處理單元,各系統如果分別采用各自的時鐘源,很難確保時鐘的統一與同步性,為信息的同步交換效率埋下了隱患,而且從工程中來看,不光增大了系統的設計分復雜度,擴大了電路布板面積,而且引入了多處的干擾源,為此,系統從總體設計上,依據FPGA豐富靈活的內部時鐘資源,提出采用如圖5所示方法,將FPGA各分時鐘作為其他給分系統的時鐘源,從而簡化了電路設計,提高了時鐘的一致性與可靠性。

評論