基于CYUSB3014 USB3.0總線開發技術

當為寫命令時,CYUSB3014需要將從DDR2中讀取的數據發送出去;當為讀命令,讀取CYUSB3014傳遞過來的數據,流程圖如圖4所示。圖5、圖6分別為同步寫入和讀出數據的時序圖。由于讀寫最大包為1024字節,所以實際每一包傳輸需要256個周期。圖中的輸入/出DQ數據為測試數據模塊和PC機產生的測試數據,RX即UART_RX信號。

3.3.2 測試數據模塊

當計算機向FPGA發出讀命令時,FPGA產生測試數據。32位數據,高16位為0,低16位循環計數,發送一個周期后,自動清零。

批量(bulk)傳輸時的最大包大小為1024字節,因此測試數據在0~255之間循環變化。

產生測試數據后,數據傳輸流程為DATA->

DDR2->FIFO->CYUSB3014->PC機,實現了將測試數據上傳到PC機的功能。

3.3.3 DDR2接口模塊

該部分直接負責外圍DDR2接口,利用FPGA的DDRII SDRAM IP核實現,按照DDR2芯片MT47H64M16HR來設定控制器的時序參數,控制器根據這些參數值生成滿足MT47H64M16HR時序的接口,再由DDR2模塊進行讀寫控制。

3.4 應用程序的設計

應用程序由VC++編寫,利用與設備驅動關聯的API與設備聯系。CYPRESS公司提供了完整的API庫,配合使用其提供的通用驅動程序,可以便利地調用控制USB設備。應用程序的主要功能是發送命令,并將USB輸入數據保存下來,程序主要界面如圖6所示。

4.測試結果及分析

4.1 寫入數據測試

當應用程序向USB發出寫命令時,FPGA產生測試數據并傳給FX3以便上傳給PC機。

采集1000MB的數據進行記錄,以便在MATLAB中進行分析。

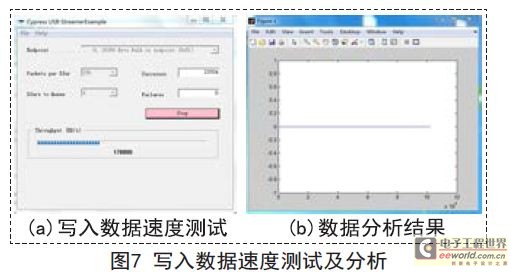

CYPRESS官方開發包中自帶了streamer軟件進行速度測試。在Endpoint選項中選擇Bulk in endpoint端點(Bulk Out對應的是PC機向FPGA寫數據)。由于批量傳輸時的最大包為1024字節,因此需要將Packets perXfer設置為256或以下,Xfers to Queue置為4。不同的USB3.0控制器,速度的測試結果會有所不同。如圖7所示是在64位WIN7系統下的測試及分析結果。如圖7(a)中所示,經過一段時間的速度測試,23704個成功包,0失敗,往P C中寫入數據的速度能夠達到178800KB/S,即1.43Gbps。為了驗證數據的正確性,在MATLAB中對采集的8.0Gb數據進行分析。由于測試數據是0~255之間循環變化,因此可以根據每一包數據的數據差是否為1來判斷數據的正確性,當不為1時報錯。

如圖7(b)所示,讀取的數據是正確的,沒有發生丟數或錯數的情況。

4.2 讀出數據測試

類似的,當應用程序向USB發出讀命令時,同時會產生一組有規律的測試數據,并傳送給CYUSB3014,FPGA直接讀取數據。如下圖8(a)所示是讀入速度測試結果,18252個成功包,0失敗,往USB中寫入數據的速度能夠達到179000KB/S,即1.432Gbps。在FPGA中記錄下隨機采集的32k數據并進行分析,同樣的可以根據數據間的差來判斷數據的正確性,如圖8(b)所示,寫入的數據時正確的,沒有發生丟數錯數的情況。

5.結束語

本文在FPGA和CYUSB3014的基礎上,對USB3.0進行了開發應用。鑒于本文的系統架構,雖然測試數據都是FPGA內部產生,但是對于實際使用高采樣率AD的數據采集系統具有很大的借鑒意義。

評論