測量位置的PSoC微控制器與LVDT

為使PSoC開關電容帶通濾波器產生最高保真度的正弦波,要用盡可能高的過采樣速率,因數約為33,即每個正弦波周期33步。得到的正弦波平滑得足以驅動能衰減所有殘余高階諧波的LVDT。采用一個可變增益放大器標定PSoC的內部電壓基準,就可以在方波濾波前對其波幅作粗略的控制。為了補償波形的直流偏移電壓,放大器對2.6V內部模擬接地基準進行緩沖,并驅動用作LVDT模擬地回路的輸出腳。

LVDT輸出包括一個幅度可變的正弦波電壓,其相對于正弦波激勵電壓的相位角要經受一個相當大的可變移位,有時相移要超過180。。LVDT的一個信號驅動PSoC的一個可變增益放大器,其輸出送至一個開關電容低通濾波器,并跟隨一個用于同步整流的調制器。整流后的信號驅動一個輸出腳,以及一個PSoC的開關電容ADC。

將LVDT輸出加在同步整流器上,后跟隨一個低通濾波器,這樣產生一個直流電壓,它可以送至ADC或直接驅動一個模擬反饋控制系統。在PSoC微控制器中,連接到ADC的低通開關電容濾波器需要相同的采樣時鐘來驅動兩個電路,因此,PSoC 11位Δ-S ADC的轉換速率大約是低通濾波器角頻率的一半。同步整流產生的紋波頻率是激勵頻率的兩倍,因此更容易用低通濾波器去除。將低通濾波器的角頻率重新確定為激勵頻率的三分之一,就可以在等于或低于1 LSB(最低有效位)標準偏差下,使LVDT輸出的測量達到11位分辨率。

用作為計數器鏈配置的邏輯電路塊將 PSoC 24 MHz 內部系統時鐘分頻,就得到開關電容器模擬電路塊需要的所有數字時鐘信號。在加電或復位之后,PSoC的CPU配置所有可配置的模擬與數字電路塊,并開始運行。以后硬件便能夠激勵LVDT并以每秒500次采樣速率測量其輸出,無需CPU的進一步干預。當 PSoC CPU運行在12 MHz時,處理ADC內部活動以及中斷只消耗不到3%的CPU資源。

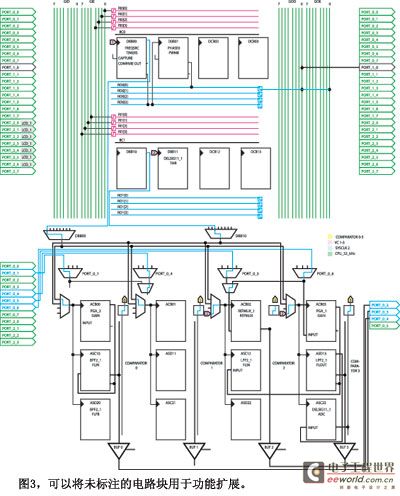

對于計算LVDT位置以及在LCD模塊上以文本形式顯示結果時有大量PSoC資源可用。有四個模擬電路塊、五個邏輯電路塊和很多I/O腳都可以用于支持更高要求的應用。圖3顯示了附加功能可以使用的配置塊。

評論