使用邏輯分析儀快速發現數字系統的問題

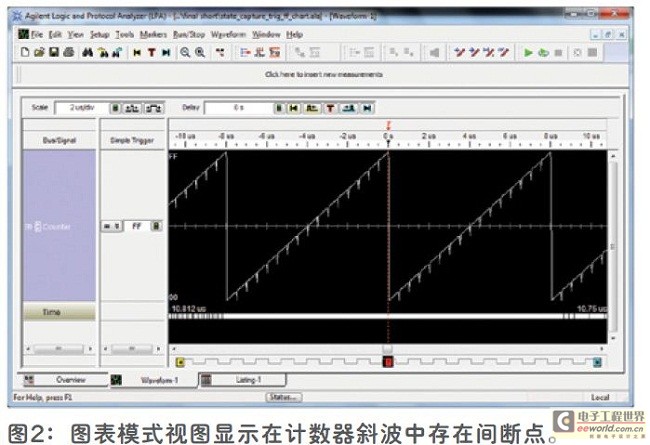

通過更接近的觀察您可以看到,計數器的最低有效位從十六進制值F跳變到0時會出現間斷點。例如,計數器從十六進制值DF跳變到E0、從EF跳變到F0以及從FF跳變到00時都會出現問題。

通過異步捕獲進行計時驗證

通過異步捕獲進行計時驗證,可對數字設計進行更深入的分析。通過這個步驟,可以辨別系統中存在的問題是功能問題、計時問題還是兩者同時存在。

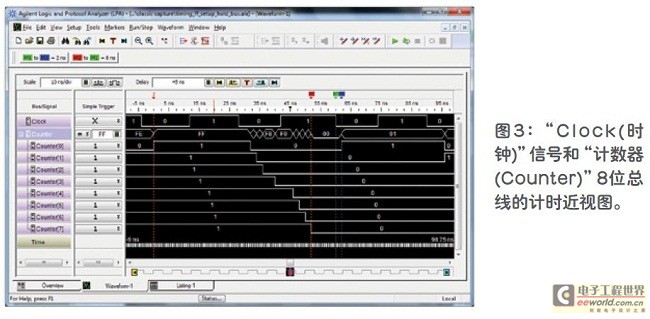

在此模式中,對時鐘信號和數據信號進行采樣和查看至關重要。另一個標簽定義為“Clock(時鐘)”,選擇適當的邏輯分析儀時鐘輸入線路(該線路已經實際連接到計數器電路時鐘信號輸出端)。最簡單的觸發設置是在Waveform窗口中,將“FF”值輸入到Counter總線旁邊簡單的觸發菜單中。

使用這種觸發進行的異步捕獲如圖3所示。觸發事件在跡線的左側,可以看到數值跳變到十六進制的“00”。在此模式中,您可以看到被測件每條線路上的信號計時,其詳細程度達到邏輯分析儀采樣電路分辨率的水平。假設數據在時鐘線路的上升沿之前變得穩定和有效。更進一步查看時鐘上升沿附近的計數器比特值,您必須選中復選框查看是否滿足了時鐘和數據之間的基本設置和保持要求。

查看時鐘上升點(計數器總線應已經從FF跳變到00)處的跡線,您可以看到非常明顯的問題。在該點上,數據總線還沒有穩定在00值上。事實上,它顯然是在時鐘下降沿附近變得穩定。設計計時中出現了錯誤。將游標分別放置在時鐘下降沿(M1)、穩定總線值00(M2)起始端和穩定總線值00(M3)終止端上。簡單的計時測量顯示了設置時間(M1-M2)和保持時間(M3-M1)相對于時鐘下降沿的數值。

可提供幫助的觸發

查找設計中存在的問題絕非易事。設置適當類型的觸發是探查設計流程問題根源的關鍵。一種最重要的觸發類型是“超時觸發”。邏輯分析儀可監測重復性的、預期會出現的目標系統行為,如果該行為在某個預定時間范圍內沒有出現,則邏輯分析儀進行觸發。當目標系統的數據總線鎖定或“暫停”在固定數據值,而時鐘繼續運行時,超時觸發非常有幫助。

總結

雖然數字系統體系結構正在發生革命性的變化,包括過渡到面向串行總線協議的總線結構,但是目前的許多設計仍在采用基本的并行總線體系結構。通常,設計人員必須對這些總線進行分析,以便進行設計驗證或查找設計缺陷。如果知道如何使用同步和異步捕獲模式以及智能觸發,可以顯著加快設計從調試到上市的過程。

評論