基于FPGA的飛行模擬器通信接口設計是什么樣的?

2.2 數據發送邏輯

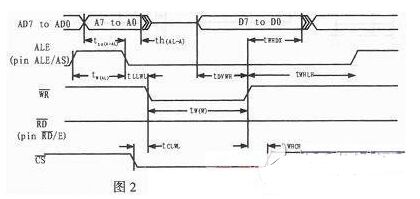

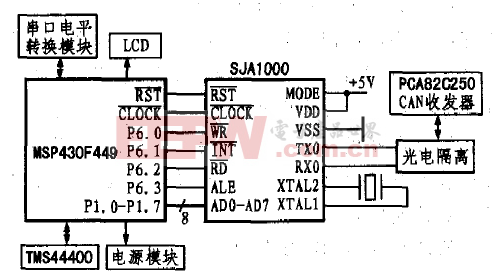

數據發送邏輯需要FPGA通過模擬總線的方法對SJA1000進行控制,SJA1000的發送緩沖區的寄存器共有11個字節,其中前3個字節分別是幀信息字節和兩個標識碼,后8個字節是數據。發送時,用戶需要將待發送的數據按特定的格式組合成一幀報文,送入SJA1000的發送緩沖區中,然后啟動 SJA1000發送即可。需要注意的是,在向SJA1000發送緩存區送報文之前,必須先判斷發送緩沖區是否鎖定,如果鎖定則等待;判斷上次發送是否完成,如未完成則需等待發送完成。總線控制器寫周期的時序圖如圖2所示。

2.3 數據接收邏輯

與數據發送邏輯類似,從接收緩沖區中讀取一條報文也需要連續讀取11個字節,數據接收邏輯除了正常的報文數據接收,還要實現其他情況的處理。對接收緩沖區的數據讀取完畢后要釋放CAN接收緩沖區。圖3所示為總線控制器讀周期的時序圖。

在FPGA程序編寫時,采用狀態機完成邏輯的設計,分別包括初始化狀態、空閑狀態、查詢狀態、數據接收狀態、數據發送狀態。

3 結論

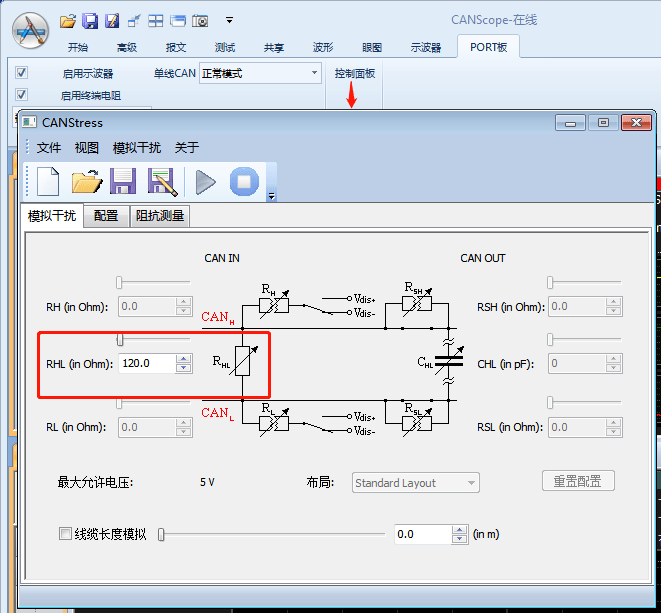

在系統設計過程中,采用ALTERA公司的EP1C6型FPGA進行設計,在Quartus II環境中利用Verilog HDL編程產生SJA1000的片選信號、地址鎖存信號以及讀寫信號等,這些信號共同驅動SJA1000完成數據的發送和接收。在采用FPGA實現對 SJA1000的邏輯控制過程中,采用Quartus II中的SignalTap II Logic Analyzer工具對FPGA各接口信號進行了測量,經檢查各種邏輯均符合SJA1000的接口時序要求。

基于FPGA的飛行模擬器通信接口設計主要由Verilog語言進行描述,易于修改和移植,同時由于FPGA的I/O豐富,還可以將模擬器中一些常用的開關量連接到FPGA上,這樣就可以將多種功能集成在一個FPGA上,相較于采用單片機控制SJA1000實現CAN總線通信,本設計方案可擴展性好,穩定性高,能降低成本、系統體積及功耗,在飛行模擬器領域中具有廣泛的應用前景。

評論