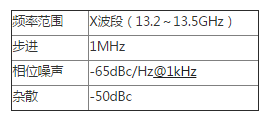

基于HMC704LP4的一種X波段跳頻源設計方案(二)

4 測試結果與結論

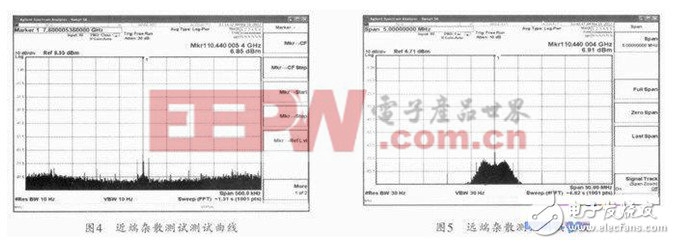

采用Agilent頻譜儀N9030A和信號源分析儀E5052B分別對該跳頻源的雜散、相噪和跳頻時間進行測試。相位噪聲測試曲線如圖3所示,測試頻率為10.47 GHz,相噪指標為-96dBc/Hz@1kHz;雜散測試如圖4、圖5所示,測試頻率為10.44 GHz,圖4為近端雜散、圖5為遠端雜散。雜散優于-70dBc.跳頻時間測試的是9.9 GHz到10.93 GHz的跳頻時間,約為36 μs.

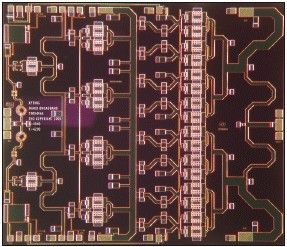

該跳頻源高于指標要求,體積為60x40×19mm3,且性能穩定可靠。經驗證該設計方案可應用于同類型的頻率頻率源設計當中去,具有實際的指導意義。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

分頻器相關文章:分頻器原理 鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理

評論