低功耗6管SRAM單元設計方案

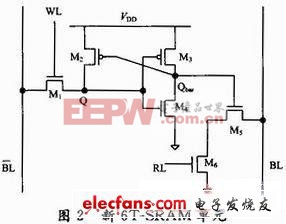

靜態噪聲容限SNM是衡量存儲單元抗干擾能力的一個重要參數,其定義為存儲單元所能承受的最大直流噪聲的幅值,若超過這個值,存儲節點的狀態將發生錯誤翻轉。隨著數字電路不斷發展,電源電壓VDD逐漸變小,外部噪聲變得相對較大。如圖1所示的6T-SRAM,在讀操作中有一個從存儲節點到位線BL的路徑,當存取管開啟,BL和存儲節點直接相連。因此,外部的噪聲很容易破壞數據,噪聲容限受到前所未有的挑戰。

2 新型6T-SRAM存儲單元簡介

針對以上問題,提出一個新型6T-SRAM存儲單元結構,如圖2所示。NMOS管M5和M6負責讀操作,NMOS管M1,M4,PMOS管M2,M3完成寫操作,讀/寫操作的時候只有1個位線參與工作,因此整個單元功耗減小很多。

(1)空閑模式

在空閑模式下,即讀操作和寫操作都不工作的情況下,當O存在Q點時,M3打開,Qbar保持在VDD,同時M2,M4是關閉的,此時Q點的數據0可能受到漏電流IDS-M2漏電堆積,從而在Q點產生一定電壓,甚至可能導致Q點數據翻轉,產生錯誤邏輯。因此要利用M1管的漏電流,主要是M1的亞閾值電流,為了這個目的,需要在空閑模式下將位線

拉到地,同時將字線WL保持在亞閾值工作的條件下,這樣就可以無需刷新正確存儲數據0。當1存在Q點時,M4,M2打開,在Q和Qbar之間有正反饋,因此Q點被M2管拉到VDD,Qbar被M4管拉到地,但是此時M1管是處在亞閾值條件下,因此有一條路徑從VDD到

,這會導致Q點數據不穩定,甚至有可能翻轉,由于流經M2的電流遠遠大于流經M1的電流,數據相對還是比較穩定的。另一條位線BL拉到地,在空閑模式下讀路徑這端漏電流很小,可以忽略。

(2)寫循環

寫1操作開始,WL高電平打開M1管,讀控制管RL關閉,

充電使得

手機電池相關文章:手機電池修復

評論