利用IBIS模型研究信號完整性問題

本文是關于在印刷電路板 (PCB) 開發階段使用數字輸入/輸出緩沖信息規范 (IBIS) 模擬模型的文章。本文將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定 PCB 設計解決方案。請注意,該提取值是 IBIS 模型不可或缺的組成部分。

圖 1 錯配端接阻抗 PCB 裝置

信號完整性問題

當觀察傳輸線兩端的數字信號時,設計人員會吃驚于將信號驅動至某條 PCB 線跡時出現的結果。通過相對較長的距離,相比瞬時變化信號,電信號更像行波。描述電路板上電波行為的較好模擬是池中波 (wave in a pool)。紋波穿過池順利傳播,因為體積相同的兩組水具有相同的“阻抗”。然而,池壁的阻抗差異明顯,并以相反方向反射波。注入 PCB 線跡的電信號也出現相同的現象,其在阻抗錯配時以類似方式反射。圖 1 顯示了錯配端接阻抗的一個 PCB 裝置。微控制器即 TI MSP430? 向 TI ADS8326 ADC 發送一個時鐘信號,其將轉換數據發送回 MSP430。圖 2 顯示了該裝置中阻抗錯配所形成的反射。這些反射在傳輸線跡上引起信號完整性問題。讓一端或者兩端的 PCB 線跡電阻抗相匹配可極大地減少反射。

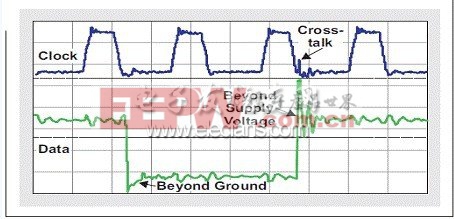

圖 2 圖 1 中錯配端接阻抗促發反射

要解決系統電阻抗匹配問題,設計人員需要理解集成電路 (IC) 的阻抗特性,以及起到傳輸線跡作用的 PCB 線跡的阻抗特性。知道這些特性,讓設計人員能夠將各連接單元建模為分布式傳輸線跡。

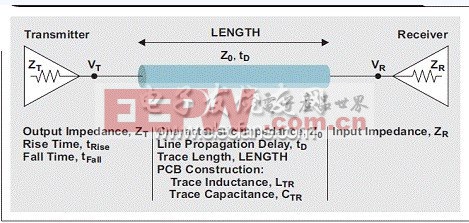

傳輸線跡為各種電路服務,從單端和差分端器件到開漏輸出器件。本文主要介紹單端傳輸線跡,其驅動器有一個推拉輸出電路設計。圖 3 顯示了用于設計該舉例傳輸線跡的各組成部分。

圖 3 實例單端傳輸線電路

另外,還需要如下 IC 引腳規范:

發送器輸出電阻 ZT (Ω)

評論