基于門控時鐘的低功耗電路設計方案

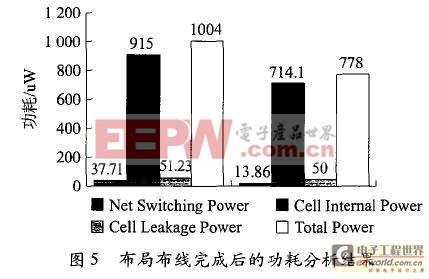

由圖5可知, 采用門控時鐘技術后的設計總體功耗下降了22. 6 %。其中, 開關功耗下降了63. 2 % ,內部功耗下降了21. 9 %,體現了引入門控時鐘技術的優勢,因為門控時鐘主要用于降低動態功耗,泄露功耗略有下降。總功耗由原來的1 mW降低至778 uW,功耗降低效果非常明顯。除此之外,芯片核的面積也略有減小。

3 結語

越來越多低功耗設計方法的出現為低功耗設計提供了無限的空間。門控時鐘技術作為當前比較成熟的一種低功耗方法,已經得到普遍應用。本設計全面講述了門控時鐘的后端實現方法,并提出了一種門控控制項的設置方法,解決了由其引起的時鐘偏移問題,對VLSI深亞微米低功耗電路物理層的實現有一定的實用價值。

評論