多鎖相環和擴頻時鐘在數字娛樂設備中的設計應

1. 高清電視系統中采用多種頻率的需要——不同的標準和接口

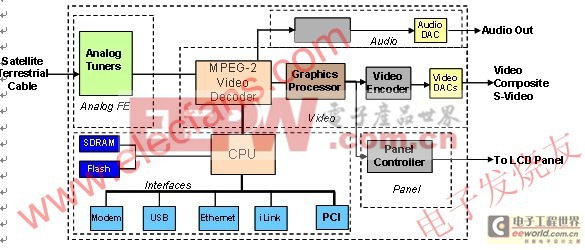

圖1所示為液晶電視機天線的基本原理圖,簡單地說明了數字電視將輸入的數字數據流處理成適于用戶起居室內電視機使用的正確音頻和視頻格式的流程。

Satellite Terrestrial Cable衛星地面電纜

Analog Tuners模擬天線

Analog FE模擬前端

MPEG-2 Video DecoderMPEG-2視頻解碼器

MPEG Audio DecoderMPEG 音頻解碼器

Audio DAC音頻數模轉換器

Audio音頻

Audio out音頻輸出

Graphics Processor圖形處理品

Video Encoder 視頻編碼器

Video DACs視頻數模轉換器

Video Composite S-Video視頻復合S-Video端子

Video視頻

Flash閃存

Panel controller面板控制器

To LCD Panel接至液晶顯示屏

Panel顯示屏

Interface接口

Modem 調制解調器

圖1:常見液晶電視機體系架構

調諧電路板上加入了多個子系統。各項基本功能從廣義上可以歸類到以下幾種模塊下:

1.模擬前端(解調器)

2.音頻/視頻編碼和解碼(MPEG視頻解碼器/MPEG音頻解碼器)

3.各類接口

4.顯示屏

上圖中所顯的所有模塊幾乎都需要時鐘信號。CPU要求的時鐘信號典型范圍為30 – 100MHz。MPEG標準要求采用基于27MHz的時鐘輸入。其中存在需要解碼器和編碼器同步的必要功能,而這項功能由VCXO(電壓控制晶體振蕩器)來實現。對于作為數模轉換器(DAC)時鐘源的音頻時鐘,其ppm要求極為嚴格。這些頻率取決于采樣頻率和過采樣比率。對于各類接口來說,時鐘信號由各自的標準來決定,諸如USB、以太網、調制解調器、PCI、PCIExpress、SATA等等。

顯示屏的時鐘取決于屏幕尺寸以及顯示標準(高清(HD):1080i、1080p、720p;標清(SD):NTSC、PAL)。屏幕控制器子系統的基本系統是將輸入圖像數據轉換成實際屏幕尺寸,例如,采用74.17582418 MHz等時鐘。

2. 電視機體系架構和時鐘樹的實現

目前,設計者不得不在設計前期做出的一項關鍵決定就是信號格式,包括模擬信號或數字信號。幾年以前,電視機的信號鏈路還是主要以模擬信號為基礎,而如今,更為常用的是數字音頻數據通路。數字和模擬通路均各自存在著一些固有的優缺點。但是,目前存在著一種全球性的必然發展趨勢,即要求所有信號傳輸都采用數字技術,該趨勢將分階段實現。

高清電視的傳輸采用了數字信號,所以,新出品的電視機趨向于采用數字通路。采用數字傳輸方式的優點在于對噪聲的容錯性很高。另一方面,模擬信號易受到噪聲的影響。電路板設計者需要在布線時加特別關注,采用擁有更優信噪比(SNR)性能的差分信號,或者運用屏蔽技術來避免信號品質降低。

傳統的時鐘樹設 計方式:這種方式針對每一種頻率要求采用了分立的晶體/晶體振蕩器(XO)。這種方式的好處在于,時鐘可以布置在非常靠近元器件的位置,使布線變得簡潔。但是,這種方式的缺陷在于,每一個晶體/晶體振蕩器元件都必須提前從供貨商處采購,從而不允許在最后階段做出設計變更。如果有一個頻率發生了變化,也要求有很長的交貨周期,從而導致整個進度的延遲。

硅芯片時序解決方案:近10多年以來,基于鎖相環的時序解決方案的流行度已經超過了傳統時鐘方法。硅芯片時序解決方案供貨商能夠提供分立晶體和晶體振蕩器元件所不支持的多項功能,從而可應用于復雜的系統設計。這兩種設計方式之間的折衷處理將在下文進行討論。轉向采用這種體系架構的客戶所獲得的主要益處在于,它賦予了客戶的設計方案靈活性并節省了成本。

3. 與分立晶體/晶體振蕩器相比,采用鎖相環硅芯片時序解決方案的優勢

1.成本——消費類產品市場領域的重要決策的驅動要素之一就是成本。每一次體系架構的變動都必須經濟而劃算,這樣才可以實施架構轉變,所付出的投資才是合理的。硅芯片時序解決方案最具吸引力的優勢在于,通過將若干個晶體/晶體振蕩器集成到一起,可以降低整體物料清單成本,并保持性能水平,或在某些情況下提升性能水平。在如上圖所示的典型電視機天線電路板中,采用了5-6個分立晶體(每個成本為0.12 – 0.50美元),而如果一個能夠提供上述頻率的可編程功能的硅芯片時鐘發生器的成本低于2.00美元,則就會真正為電路板增值。除了成本是晶體/晶體振蕩器集成的主要推動要素,另外還有一些能夠為OEM商和最終用戶所感受到的其它優勢。

2.可靠性——晶體是基于石英的元器件,比起基于鎖相環的時序解決方案來說,晶體的故障率較高。從系統中每減少一個晶體都有助于提高整個系統的可靠性。集成度高還能夠減少電路板上的元器件數量,獲得最高的穩定性并實現更低的返修率。

3.晶體可用性——頻率范圍在10-40 MHz之間的晶體很容易做到。但高于40 MHz以上的高頻晶體在制造上難度更高并且需要采用特殊的制造技術。這種晶體屬于高階泛音晶體,成本范圍在1-10美元之間。這些高階晶體較難購得。而硅芯片時序解決方案能夠采用單個低頻晶體(或者可以使用時鐘基準信號)來生成多個高頻輸出。

4.晶體老化——晶體本身容易出現老化現象,每隔幾年會出現+-2ppm至+-5ppm的誤差。這種老化現象的原因在于晶體材質內部以及晶體表面之上存在的雜質以及晶體材料與沉積電極之間的機械應力。老化可能導致使用晶體的系統性能緩慢下降。在使用晶體時,長期頻率漂移已經成為常見的問題。而基于鎖相環的硅芯片時序解決方案能夠在產品整個使用壽命內保持精確度。

5.可編程性——基于鎖相環的時鐘發生器擁有內置可編程性,可以在設計階段提供一定的靈活性。這些可編程特色不僅包括了輸出頻率的改變,而且能夠改變驅動信號強度設置值、擴頻百分比、通過引腳編程實現頻率選擇,這些意味著同一個輸出端可以根據需要提供不同的頻率。系統內置的可編程性可以采用串行I2C接口在設計執行過程中改變一些特定參數。這一特色對于那些在多個平臺上采用同一組頻率的制造廠商是富有吸引力的。

6.減少元器件數量,節約板卡空間——采用可編程時鐘發生器有助于通過集成減少電路板上的元器件數量。系統設計者正在趨向于采用更少的元器件,以求減少由于布線和需要保持信號完整性所帶來的問題。基于鎖相環的時鐘發生器能夠采用一個低頻晶體生成若干個輸出,因此對于減少元器件總數量以及節約寶貴的板卡空間極具價值。

7.采用擴頻時鐘降低電磁干擾——電視機天線電路板典型情況下為5-7層板,并采用了專用的鋪地層以便壓低干擾。為提高系統性能和避免發生串擾、扭曲和信號完整性問題,要對多路高速信號進行精心的布線。而硅芯片時序器件供貨商通過提供擴頻等功能,減少了這些板卡設計方面的問題。例如,擴頻可以通過擴展高速信號來降低信號的峰值能量。

電磁干擾必須低于強制性標準所規定的限值,這些標準如CISPR 22或FCC Part 15 Class B。所有消費類產品必須通過嚴格的FCC規范認證才能上市。全球各地諸如美國通信委員會(FCC)這樣的管理機構會確保強制性標準得到遵守而且器件產品不能在不屬于它們的頻段內發射信號。不幸的是,存在頻率諧波的高速設計方案經常會遇到這方面的問題。擴頻是一項目前由集成電路供貨商提供的、能夠解決這一干擾問題的功能。

擴頻功能能夠減少、甚至消除對會增加物料清單成本的鐵氧體磁珠、濾波器、線圈和振流器的需要。如果系統未能通過電磁合規試驗,則需要花大力氣進行重新設計。考慮到試驗所耗費的成本以及重新進行工程設計所浪費的時間,我們會 認識到對這些問題做好通盤考慮并采取保險措施的重要性,例如提前采用擴頻功能。而擁有可編程性就可以在需要時打開擴頻功能以及在不需要時關閉該功能。這一功能在開發和測試中尤為實用。

8.庫存管理——采購團隊目前所面臨的一項主要難題是對系統采用的每

評論