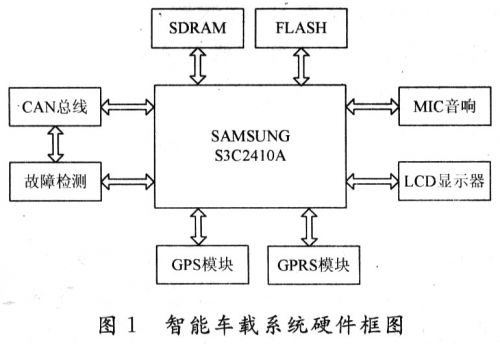

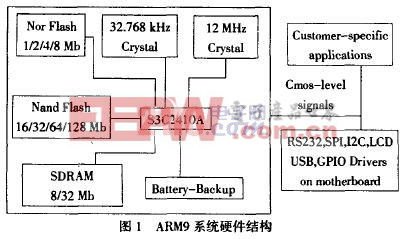

基于S3C2410A的MDB/ICP協議的實現

如果要想支持MDB協議,S3C2410A沒有mode bit可用,這樣對MDB總線上的數據判斷是地址字節還是數據字節和總線一幀數據什么時候結束在S3C2410A上無法判斷識別,這對最初制定的方案提出了嚴重的挑戰,迫不得已要對S3C2410A成為MDB/IPC協議的VMC設備的可能性進行預研,最直接的方式就是想到利用S3C2410A的可選的奇偶校驗位的值來逆推MDB設備的mode bit的值,讓奇偶校驗位來充當MDB mode bit的作用,從而來判斷出S3C2410A接收MDB設備傳送的數據是否是結束了。經過分析就可以得到表1所列的推理。

表1

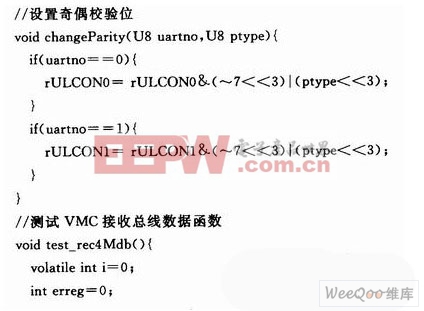

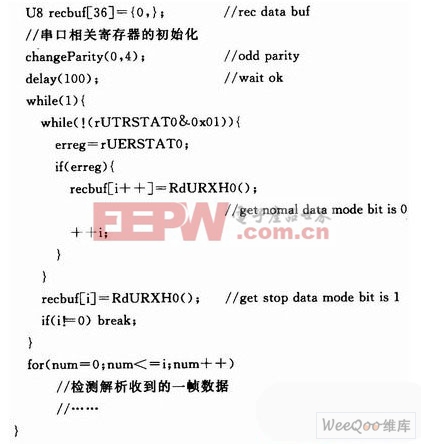

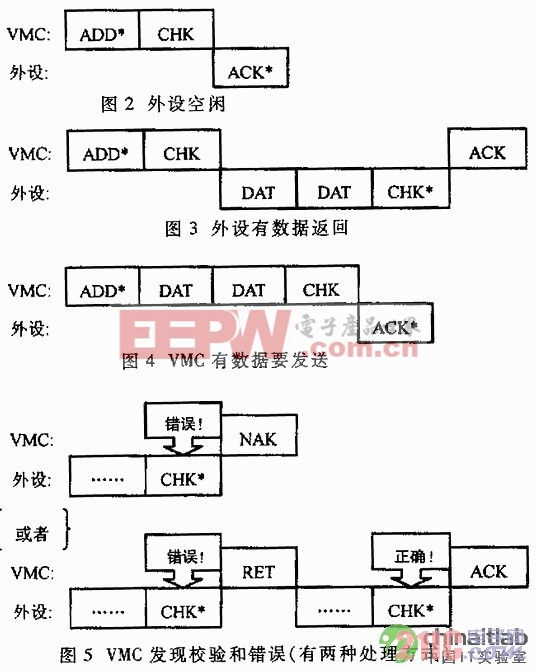

通過上面的分析,開始編寫測試程序,結果發現S3C2410A的串口設計的一個bug:當配置UART LINECONTROL REG ULCONn的BITS[5:3]為“101”,選擇evenparity接收MDB總線的數據的時候,無論是構造出來的數據1的位數為奇數個還是偶數個搭配具體的模式位,發現S3C2410A的UART ERRORSTATUS REG(UERSTATn)的bit2 frame. error位并不能準確的置位。想想S3C2410A這么流行的芯片竟然還有設計不完美的地方,幾乎要放棄的時候,本著一切皆有可能的原則,既然芯片都不可靠了,就索性測試一下,按照表1把ULCONn的BITS[5:3]設置為“100”,選擇odd parity接收數據。按常理推斷even parity的結果應該和odd parity結果是一樣的,抱著試一試的態度,構造測試代碼,結果出現了明顯的規律:當模式位為“O”的時候,UERSTATn的bit2 frame. error位可以準確的置位;當模式位為“1”的時候,UART TX/RX STATUS REG(UTRSTATn)的bit 0(receive buffer data ready)可以準確置位,正常接收數據。得到這個規律之后,2410 VMC設備就可以準確判斷出MDB設備發送過來的數據是否是收到了結束標志。另外,當VMC向MDB設備發送數據的時候,可以按照協議要求當要發送地址字節時可設置ULCONn的BITS[5:3]為“110”,代表parity forced/checked as 1來把奇偶位強制1充當模式位,地址字節發送結束之后調整ULCONn的BITS[5:3]為“111”來發送數據字節。至此,S3C2410A充當MDB VMC設備可以得到完美的解決。下面是VMC接收總線數據的部分調試代碼片段。VMC向總線發送數據相對比較簡單,有興趣的讀者可以與筆者交流探討。

結語

本文給出了一種在嵌入式處理器ARM(S3C2410A)上實現MDB/ICP協議的實現方法,在工程實踐中,證明該方法準確可靠,滿足了市場的需要,拓展了支持該協議的硬件平臺,豐富了支持該協議設備的軟件功能接口。本文的實現方法也可以應用在其他嵌入式處理器上。

參考文獻:

[1].S3C2410Adatasheethttp://www.dzsc.com/datasheet/S3C2410A_.html.

評論