基于PXA255設計的圖像采集傳輸系統

|

3 系統主要模塊的工作原理及實現

3.1 FPGA圖像采集的實現

OV9650的數據輸出采用Bayer原始數據輸出格式,每個象素同時只輸出一種顏色。奇數掃描行輸出RGRG…,偶數掃描行輸出GBGB…。FPGA負責圖像傳感器數據的采集。

上電后,系統首先對CMOS圖像采集芯片進行初始化,以確定其工作模式。這些參數受OV9650內部相應寄存器值的控制。FPGA通過控制SCCB總線來完成參數的配置。

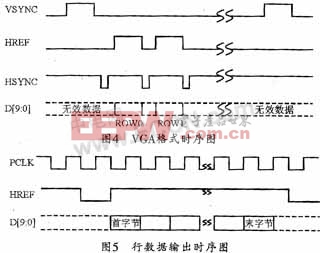

系統配置完畢后,便可進行圖像數據的采集。圖4和圖5是數據采集與輸出的時序圖。其中VSYNC是場同步信號。HREF是水平同步信號。PCLK是象素數據輸出同步信號。HREF為高時即可開始有效數據采集,而PCLK下降沿的到來則表明數據的產生,PCLK每出現一個下降沿,系統便傳輸一位數據。在HREF為高電平期間,系統共可傳輸640位數據。在一幀圖像中,即VSYNC為低電平期間,HREF會出現480次高電平。而下一個VSYNC信號上升沿的到來則表明分辨率640×480的圖像采集過程的結束。

|

3.2 FPGA與ARM的數據交換

FPGA內部用一個8 KByte雙口SRAM作為圖像存儲區。為了實現圖像數據的實時采集與處理,應使圖像數據的采集與外部圖像數據的讀取同時進行。因此本系統采用雙緩存結構。實現方法是把8 KB的SRAM劃分成兩個大小為4 KB的SRAM(設為SRAM1和SRAM2),每片SRAM一次存儲六行圖像數據。這樣,在同一時刻,一片可用于存儲圖像數據,另一片可用于外部ARM對圖像數據的讀取。兩塊SRAM存儲區乒乓式切換。當圖像數據寫滿SRAM1時,FPGA向ARM發送一個中斷信號,之后,ARM響應中斷并讀取SRAM1中的圖像數據,同時將其寫入到SDRAM中。之后,圖像傳感器的數據將寫入SRAM2,當圖像數據寫滿SRAM2時,FPGA也向ARM發送一個中斷信號。ARM響應中斷并讀取SRAM2中的圖像數據.同時將其寫人到SDRAM中。之后,圖像傳感器的數據將再次寫入SRAM1。

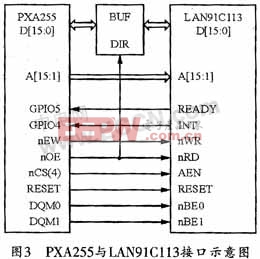

3.3 以太網數據傳輸的實現

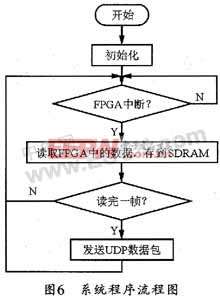

為實現圖像數據的網絡傳輸,本系統基于PXA255開發了UDP/IP協議實現程序,以將圖像數據存儲在SDRAM中。一個完整的數據幀格式包括以太網頭、IP頭、UDP頭和一行圖像數據,其系統工作流程圖見圖6所示。上電后,系統將等待FPGA中斷,如果中斷產生,則由PXA255讀取FPGA中的數據并寫到SDRAM中。然后判斷是否讀完一幀圖像數據,若讀完,則發送UDP包,并將圖像數據通過以太網發送到上位機,否則繼續等待FPGA中斷。

|

4 結束語

本文介紹了用ARM和FPGA實現的一個實時圖像采集傳輸系統的設計方案,本系統設計方案采用FPGA技術來為作物識別、雜草識別等圖像處理算法的實時實現提供了平臺。

評論