基于51單片機的編碼譯碼顯示實驗電路設計

0 引 言

在日常數字邏輯電路實驗中編碼譯碼顯示實驗電路是編碼、譯碼、顯示三個電路的綜合運用, 在數字邏輯實驗電路中具有重要的地位, 在實驗的過程中, 時常會出現顯示結果的抖動, 經研究出現這種現象主要原因是:編碼電路的編碼信號輸入采用手工撥盤方式, 產生的編碼輸入信號往往不穩定; 另外, 電路控制性能較差,不能達到自動復位, 為此有必要對現有電路進行改進,在電路的設計上采用89C51 單片機為控制電路制作而成, 自動提供穩定編碼輸入信號, 顯示結果穩定性和電路控制性能大大提升, 提高了教學實驗質量。

1 編碼譯碼顯示實驗電路的基本結構

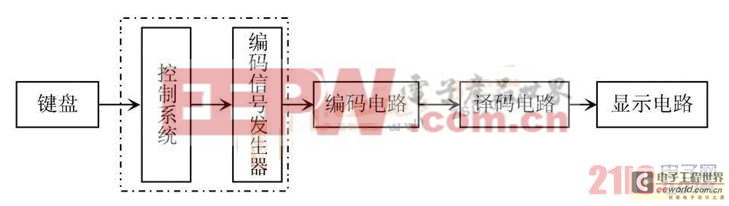

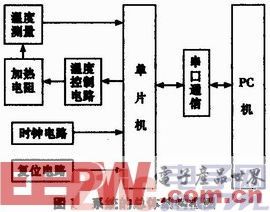

編碼譯碼顯示電路的基本結構如圖1 所示, 主要由控制電路、編碼信號發生器、編碼譯碼顯示電路等組成,控制電路產生編碼信號作為編碼譯碼顯示電路輸入信號, 譯碼電路將編碼信號轉換成對應的七段數碼顯示信號, 送至LED 數碼管顯示。

編碼譯碼顯示實驗結構圖

圖1 編碼譯碼顯示實驗結構圖。

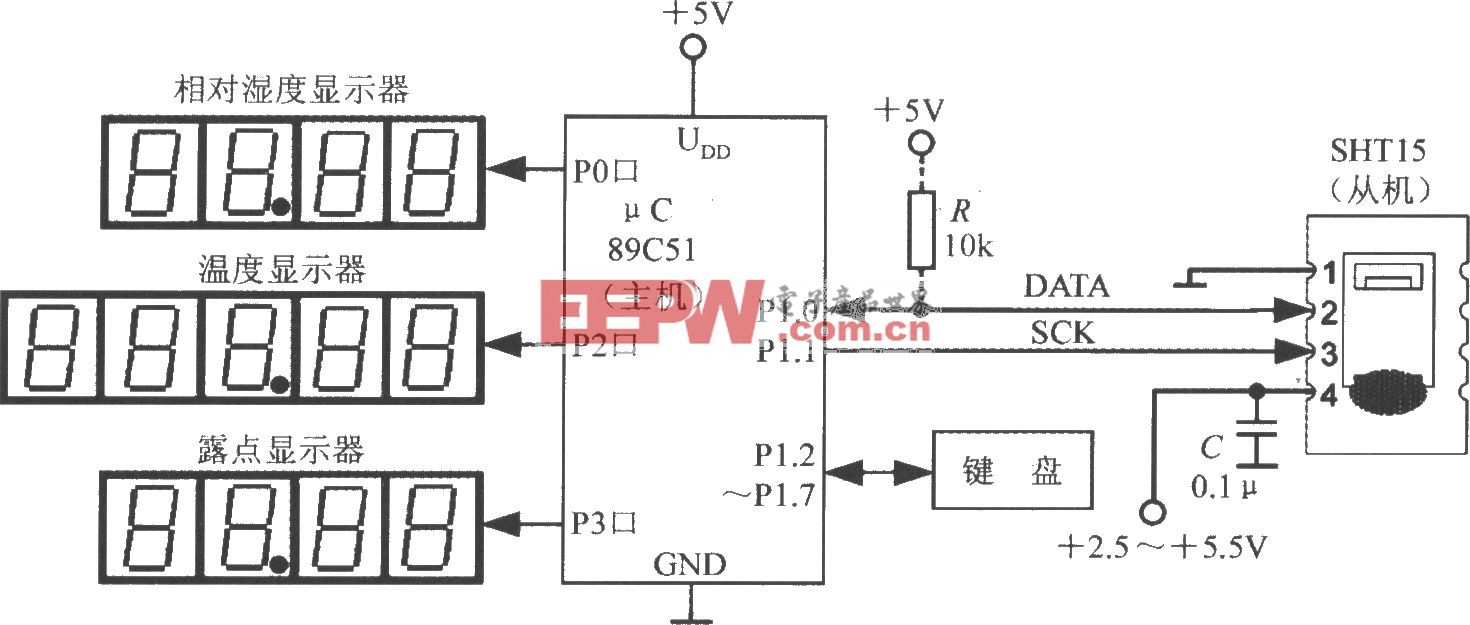

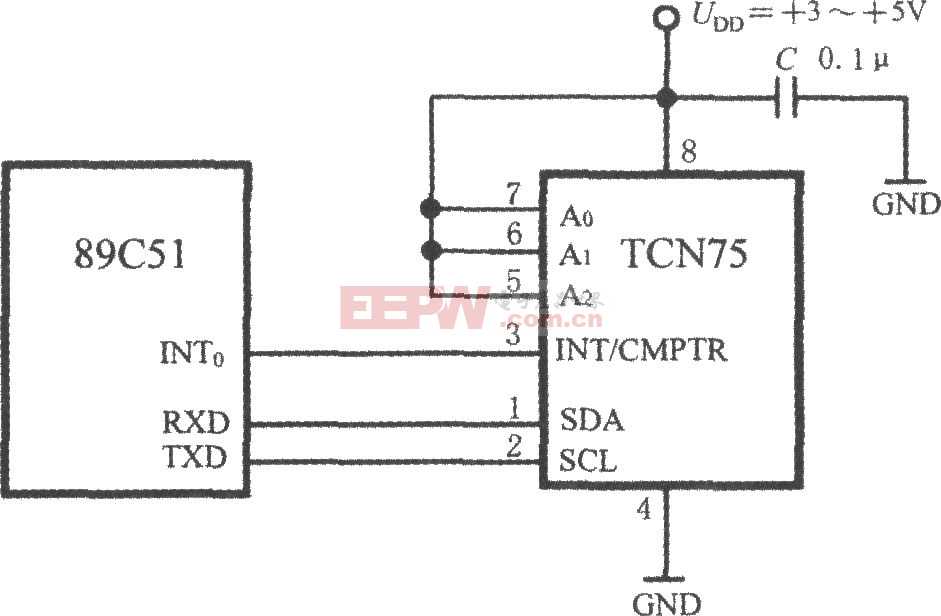

2 系統硬件設計

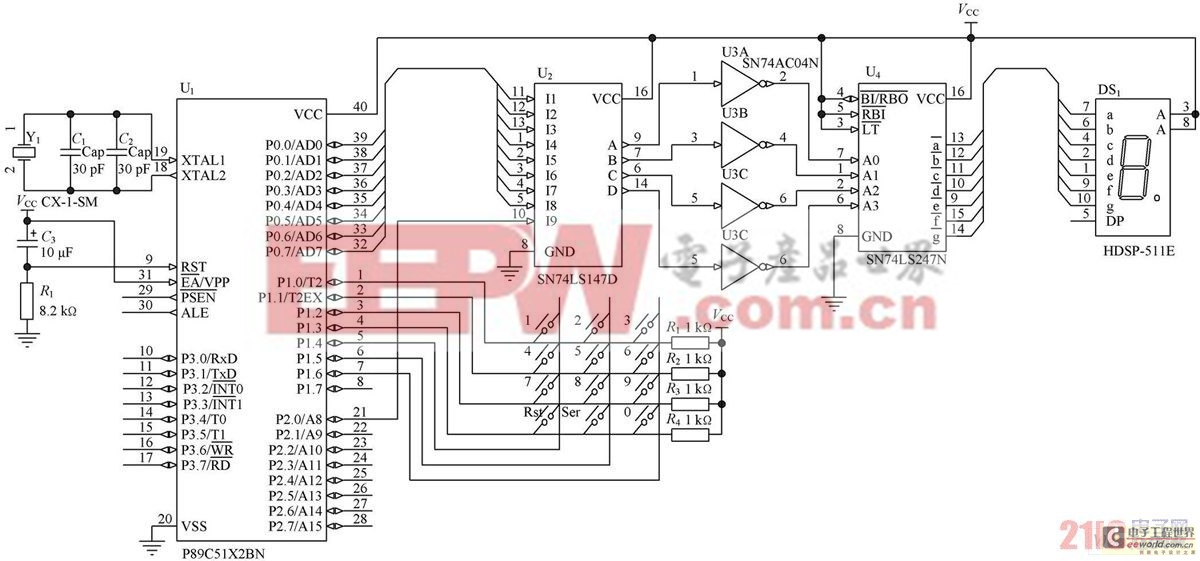

控制系統和編碼信號發生器采用89C51 單片機實現。89C51 性價比較高, 采用12 MHz 晶振, 其內部帶有4 KB 的FLASH ROM, 無須外擴程序存儲器。編碼譯碼電路沒有大量運算和暫存數據。89C51 內部的128 B片內RAM 已能滿足要求, 無須外擴片外RAM。

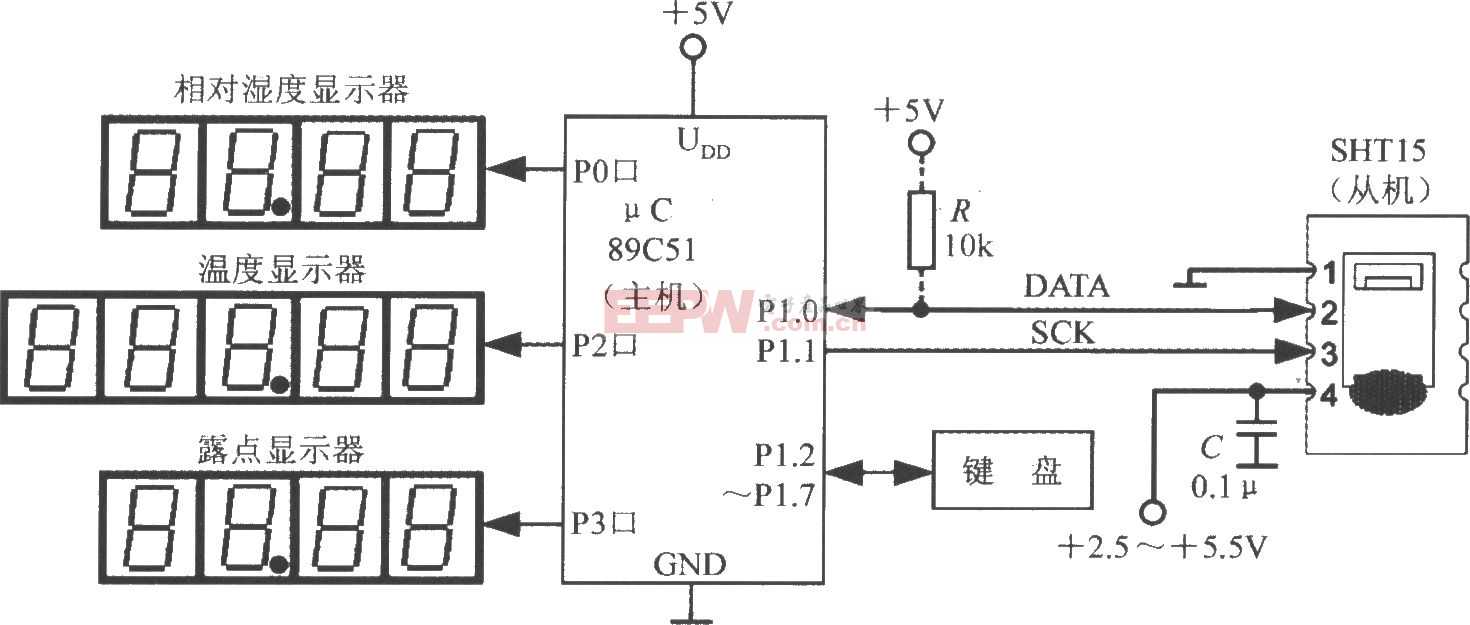

系統硬件設計如圖2 所示。

編碼譯碼顯示實驗電路

圖2 編碼譯碼顯示實驗電路。

評論