基于低成本FPGA的高清低碼流H.264攝像機SoC參考設計

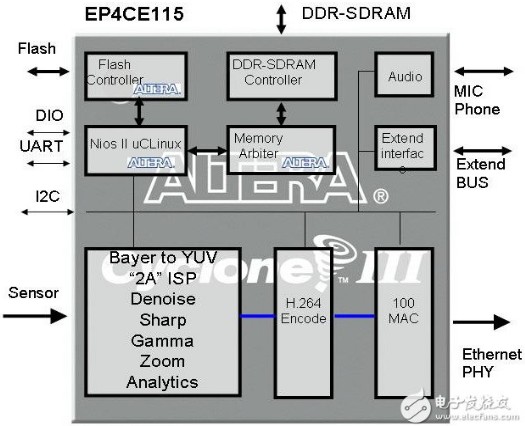

FPGA的內部結構如下圖所示:

本文引用地址:http://cqxgywz.com/article/221557.htm

圖2 FPGA的內部結構圖

FPGA的選用

在高清低碼流H.264攝像機的結構中,除了圖像傳感器、存儲器、電源和模擬接口外,所有的功能如圖像處理、H.264編碼、協議處理、參數管理、媒體流發(fā)送等都由FPGA實現,FPGA就是高清低碼流H.264攝像機的 SoC;目前世界上FPGA的生產商只有幾個,可選擇的產品也不多,要用FPGA實現高清低碼流H.264攝像機的SoC,選擇一款合適的FPGA非常重要,FPGA的選擇主要考慮三方面的因素:速度、成本和結構;每個FPGA生產商都有多個FPGA系列,每個系列的速度、性能和價格都不同,要使高清低碼流H.264攝像機SoC的成本盡可能低,應該選擇成本最低的系列,像我們選擇的FPGA是Altera公司的CYCLONE IV系列,型號是EP4CE115F23C8,CYCLONE IV是低成本系列,在同樣是低成本系列的FPGA中,CYCLONE IV的速度是最快的; FPGA的結構對圖像處理也很重要,尤其是存儲器和乘法器的數量,H.264算法是以宏塊為單位,在處理過程中必然會涉及到宏塊的輸入輸出和緩存,1個宏 塊的數據為384字節(jié)(256字節(jié)亮度數據和128字節(jié)色度數據),如果考慮到輸入輸出和處理的并行,必須設置雙份,即768字節(jié),用CYCLONE IV的1個M9K存儲塊正好,從上面的分析可以看出適合圖像處理的FPGA對內部存儲器的要求是存儲塊容量小(如1KB)、存儲塊數量多,另外,對乘法器的要求也是數量多;在我們選擇FPGA的時候,CYCLONE IV是在所有低成本FPGA中有最大的存儲器邏輯比和乘法器邏輯比,很適合做圖像處理。

圖像傳感器的選擇

為 了滿足1280x720x25fps的要求,只需要選擇百萬像素的傳感器就可以了,我們最終選擇了300萬像素的AR0331,還可以實現 1920x1088x11fps,在實現1280x720x25fps時還有電子PTZ功能,AR0331還有寬動態(tài)功能,便于攝像機以后擴充寬動態(tài)功 能。

外部存儲器

外部存儲器有2片LP DDR SDRAM和1片串行FLASH,串行FLASH用于存儲FPGA的配置數據和NIOS的數據程序,1片LP DDR SDRAM用于存儲圖像數據和編碼結果,1片LP DDR SDRAM用于NIOSII運行ucLinux。

FPGA實現的功能

FPGA作為高清H.264攝像機的SoC實現的功能如下:

① 圖像處理

● 邊緣檢測RAW插值計算

簡單的RAW插值計算會造成邊緣模糊,增加邊緣檢測判斷可以避免造成邊緣模糊;

● 3D濾波

從圖像傳感器出來的圖像包含有噪聲,去噪同時在幀間和幀內進行;

● 2D銳化

由于鏡頭等因素影響,從圖像傳感器出來的圖像需要銳化才能清晰;

● GAMMA校正

從圖像傳感器出來的圖像灰度不正確,需要做GAMMA校正,獲得正確的灰度;

● 自動曝光控制

根據亮度條件調節(jié)適合的曝光參數;

評論