基于FPGA的DDS勵磁恒流源設計

2. 2 低通濾波模塊

DDS有一個明顯的缺點,即輸出頻率越接近Nyquist帶寬的高端,采樣點數越少,其輸出的雜散干擾就越大。輸出波形具有大量的諧波分量和系統時鐘干擾。為得到所需頻段內的信號,需要在DDS輸出端加一濾波器來實現,而低通濾波器能較好地濾除雜波,平滑信號,所以低通濾波器的設計尤為重要,濾波特性的優劣對輸出信號的性能起重要的影響。

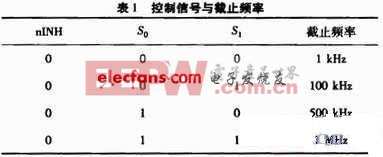

為取得較好的濾波效果,濾波器采用了由四選一模擬開關和精密運算放大器分段濾波的方式:采用巴特沃斯有源低通濾波器,該濾波器通帶內幅度很平坦,濾波電路為二階巴特沃斯低通濾波電路,濾波器頻段參數的選擇由FPGA輸出的控制信號nINH,S0,S1控制模擬開關的選通實現。

2.3 幅度控制

本設計幅度控制電路采用調節DAC參考電壓的數字化控制方法,采用兩個D/A級聯的方式,數模轉換器DAC2采用外部可變基準源,通過改變基準源的值來改變輸出的滿幅度電流值,該可變基準源通過DAC1產生。DAC1的基準電壓采用輸出電壓為1.25 V精密電壓基準芯片提供,設DAC1的幅度輸出字為N1,則DAC1的參考電壓為

![]()

設DAC2的數字輸入字為N2,則經電流/電壓轉換后的輸出電壓為

![]()

2.4 人機交互

為方便快捷地控制DDS的頻率字輸入和幅度控制,本設計采用單片機來實現對DDS信號發生器的控制。DDS的頻率字和幅度數據字位較多,而單片機輸出端口位數有限,所以單片機與FPGA之間的通信采用SPI(Serial Peripheral Interface,串行外設接口)方式,單片機將控制命令字傳送給FPGA。同時,為了輸入控制方便,添加了鍵盤和顯示系統。

3 數字閉環控制系統的實現

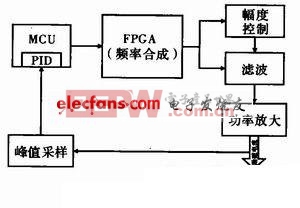

設計的勵磁恒流源主要為磁性測量儀器提供激勵電源,因而對其精度和穩定性要求高,采用電流控制型的控制策略進行閉環控制,結構框圖如圖3所示。勵磁電流幅度調整時,首先對勵磁電流進行多周期采樣,然后計算其有效值,并與輸入設定值相比較,若誤差ε在允許范圍之外,則根據誤差的實際情況,通過單片機內增量式PID算法得出了一個新的控制量,傳送給FPGA控制幅度調節經低通濾波器濾去高頻成分,再經功率放大,得到高精度的勵磁電流。

4 系統仿真與驗證分析

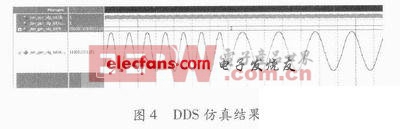

在Altera公司的QuartusⅡ環境下編譯完成,采用自上而下的設計方法,即先從系統總體要求出發將設計內容細化,最后完成系統硬件的整體設計。完成DDS設計后,通過編寫Testbench在Modelsim進行仿真。在QuartusⅡ中,設定輸出信號頻率為1 MHz,經過50 μs后改變為500 kHz進行仿真,其仿真結果如圖4所示。在Modelsim中生成的仿真數據經驗證完全正確,滿足設計需求。

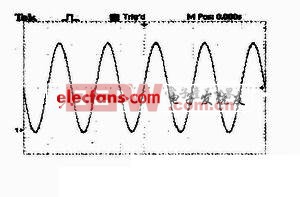

在對勵磁信號源做硬件系統測試時,首先完成系統硬件連接,并加載程序,設定輸出信號頻率為1 MHz,示波器測得實際輸出波形如圖5所示。在Modelsim環境下仿真和在硬件平臺上測試,結果表明勵磁信號源可獲得較好的設置波形,可以應用于磁性材料的測試中。

5 結束語

運用Verilog硬件編程語言結合DDS技術,利用FPGA器件強大的硬件功能,提高了系統集成度,實現了輸出信號相對帶寬寬、穩定性好;其相位累加器在一定系統時鐘和累加器位寬條件,輸出信號分辨率越小,頻率控制字的傳輸時間以及器件響應時間都很短,使輸出信號頻率切換時間較短,可以達到ns級,且頻率變化時,相位保持連續,系統采用閉環控制,勵磁電流輸出精度高,調節速度快。對磁性材料測量儀所要求的勵磁信號源而言,本設計不但滿足所有技術指標,而且集成度高、體積小、顯著地降低了成本。

評論