可編程模擬器件在接收機動態可重構結構應用

在筆者所從事的系統設計中,當模擬器件的一些性能改變但又不能及時更新調整后端的數字基帶處理時,比如濾波器由于工作時間過長引起的溫漂特性所帶來的影響,此時就可以用可編程模擬器件替代一部分前端固定模擬器件,進而可以實時的對FPGA模塊進行動態可重構操作,最終達到系統性能的最優化。

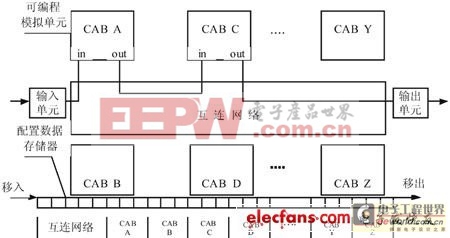

可編程模擬器件是近年來嶄露頭角的一類新型集成電路。它屬于模擬集成電路,即電路的輸入、輸出甚至內部狀態均為隨時間連續變化且幅值未經過量化的模擬信號;同時,該類器件又是現場可編程的,即可由用戶通過改變器件的配置來獲得所需的電路功能。為支持上述可編程能力,可編程模擬器件需以可編程模擬單元(CAB)和可編程互連網絡(PIN)為核心,配合配置數據存儲器、輸入單元、輸出單元或輸入輸出單元等共同構成[1](見圖1)。

圖1 可編程模擬器件組成框圖

多數可編程模擬器件在單一的+5V電源電壓下工作,額定功耗為100mW量級。由于采取了特殊的措施,其輸入、輸出線性范圍通常可達到接近滿電源電壓量程;閉環帶寬已達到數百千赫到數十兆赫;頻率失真度、共模抑制比、內部噪聲等指標也已達到中、高精度運算放大器的水平。

盡管模擬信號處理的精度低于數字信號處理方式,但仍能滿足許多重要應用對計算精度的要求,而所需的電路規模較小,成本也較低。同時利用其可編程特性,還可以實現精確的自動調諧和自動增益控制,顯著提高通信系統的抗干擾能力。

相位檢測器的實現

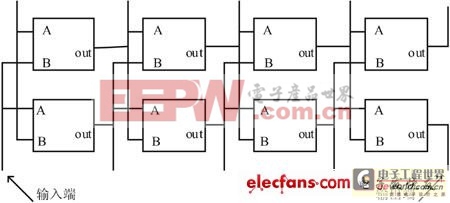

TRAC(完全可重配置模擬電路)是英國FAS公司的現場可編程模擬器件系列產品的總稱。它提供了一條從信號處理問題出發,可解決各種常見的信號處理問題。器件參考模擬計算機的運算單元并加以擴充,使器件內部的每個可編程模擬單元均具備加、減、取負、對數、反對數、積分、微分等8種運算功能,因此只需選定運算的類型和給出必要的參數,便可以很方便地完成對有關單元的設計,根本無須考慮單元電路的內部結構等具體細節。其內部各單元之間采取自左向右固定連接的形式,所有單元的輸入輸出端均引出至器件引腳上,并且允許利用各單元均具備的“直通”和“關斷”功能或者利用外接的“短路線”來修改這種基本連接[1](見圖2)。

圖2 TRAC器件結構示意圖

在筆者所從事的認知無線電硬件平臺設計中,由于需要從強信號背景環境中識別提取出微弱的信號,因而可利用TRAC器件構成相敏檢測器,并將其作為鎖存放大器的一部分。要實現這一目標,需要電路像窄帶濾波器那樣工作,除去大部分不希望要的強信號而僅允許待測的微弱信號通過。

圖3所示為相位檢測器的基本框圖。輸入信號和參考開關信號具有相同的頻率和相位。從所示的開關輸出中可望得到一個全波整流信號,而且經過低通濾波器后,便可得到和交流信號電位成比例的直流電壓輸出。在實際應用中,輸入信號可能非常小,因此還需要加入前置放大級以支持精確的檢測。因為通常需要在一定的范圍內連續改變參考信號的頻率,同時測量相應的直流輸出。同樣,若需要檢測某個單一頻率,則參考信號必須與待測輸入信號頻率相同。由于相位檢測器也對相位敏感,因此當兩個信號相位相同時會得到最大的輸出電壓。

圖3 相位檢測器框圖

相位檢測器和低通濾波器一樣需要利用兩片TRAC器件來實現。而外部元件對于放大器和濾波器都是必不可少的,所以必須對滿足條件的元件進行合理取值。

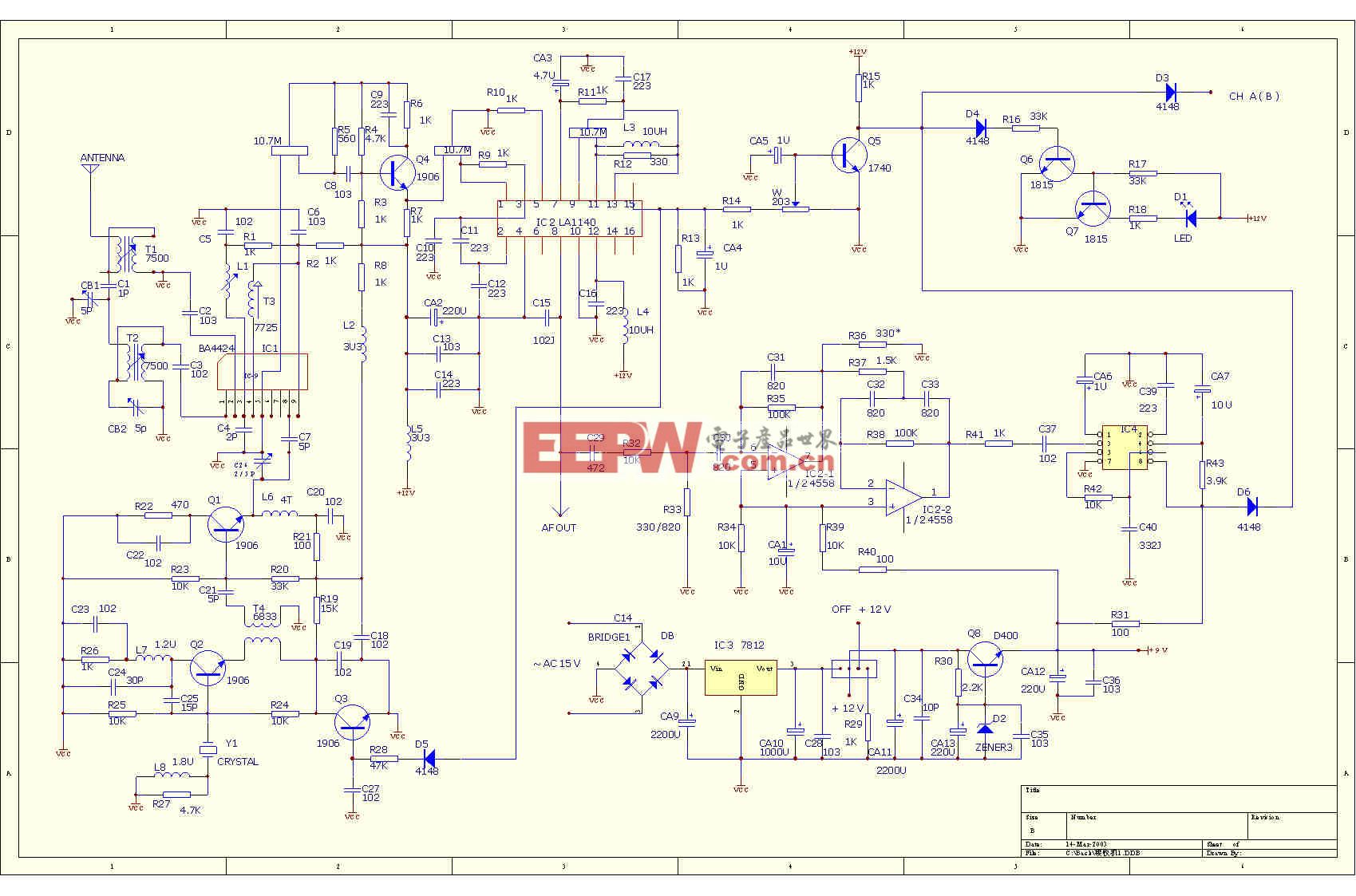

可編程ADC的實現

認知無線電接收機對其前端采用的高性能模-數轉換器(ADC)及模擬器件的要求都較高,而FPGA在基帶數字信號處理方面又迫切需要動態可重配置。為了適應以上要求,可以首先考慮使用可編程模擬器件來實現ADC,以下是兩種具體實現方法。

FIPSOC混合信號片上系統

SIDSA公司的FIPSOC混合信號片上系統是快速開發模擬、數字集成應用的理想工具。FIPSOC芯片包括內嵌的增強型8051微處理器、現場可編程門陣列(FPGA)以及一組面向信號調理和數據采集應用的可靈活配置的模擬單元。與分離的模擬、數字FPGA方案相比,采用FIPSOC混合信號片上系統,可使產品設計周期縮短30~40%。

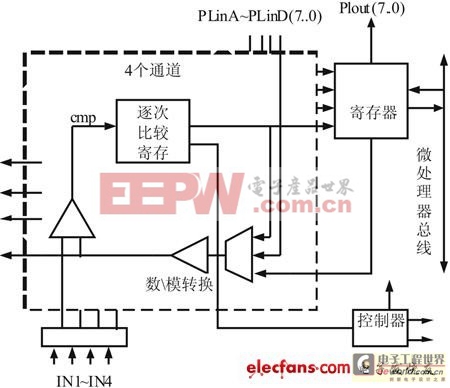

可編程的模擬、數字單元與8051的單片系統包括模擬單元、轉換單元、可編程數字單元、8051內核和該系列中的所有器件具有兼容的存儲器分布,其中轉換單元含有4路DAC(分辨率可配置為8至10位),采用逐次逼近算法,可利用這些DAC實現高達800KHz采樣率的ADC(見圖4)。

圖4 數據轉換模塊的框圖

數據轉換模塊包含4個8位的逐次比較寄存器(SAR),它可以和內部的DAC聯合工作,以獲得模/數轉換。

每一個通道有一個獨立的SAR,它接收逐次比較的結果,并驅動對應的DAC,每一個通道的轉換可以獨立進行。當轉換模塊編程為9或10位ADC轉換時,相應的SAR形成組:9位ADC時,SAR1和SAR2為一組,SAR3和SAR4為一組;10位ADC時,所有4個SAR形成一組。這時,成組的SAR各自工作1至2個周期,在轉換結束時,SAR將其內容寄存在輸入/輸出寄存器中,并使能中斷產生模塊。在連續轉換模式下,將啟動下一次轉換。在轉換過程中,可編程邏輯模塊可以獨立發布轉換命令,這將給本次以及下一次轉換帶來錯誤。在連續轉換模式下,這將導致致命錯誤,因為錯誤是可以傳遞的,并將得到不可預料的結果。

其控制部分是一個標準的8051微處理器。復合后,8051核首先對可編程元胞進行配置,配置完畢后可以當作一個通用的微處理器使用。為了更好的支持FIPSOC的動態可重構特性,已對其指令和功能單元做了一些改進。

評論