基于GAP技術的網(wǎng)絡隔離設備的研究與設計

3.3 SDRAM IP核的

應用

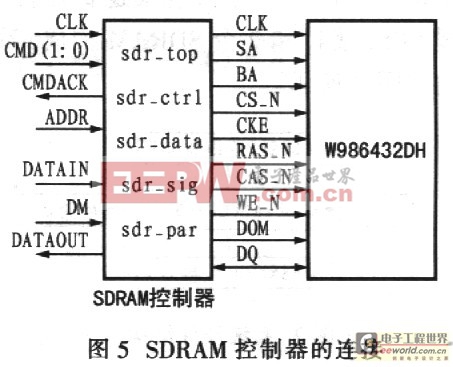

SDRAM是一種高速同步動態(tài)隨機存儲器,在嵌入式系統(tǒng)中,SDRAM因其價格低、體積小、速度快,容量大等優(yōu)點而逐漸成為一種主流器件,但SDRAM的控制邏輯復雜,時序嚴格,使用不便,需要控制器提供正確命令來完成其初始化、讀寫和刷新等工作。SDRAM控制器根據(jù)SDRAM的內部狀態(tài)轉化圖進行設計,而且很多大公司都提供標準SDRAM控制器的IP核參考設計。筆者選用了WINBOND公司的W986432DH型SDRAM,它采用512 Kx4x32位架構,由4個BANK構成,每個BANK對應4 M字節(jié),按行和列尋址,W986432DH的引腳分為控制、地址和數(shù)據(jù)信號三類。其控制器選用Lat

8dr_ctrl模塊根據(jù)SDRAM內部狀態(tài)轉化關系建立2個有限狀態(tài)機和1個計數(shù)器,能產生正確的中間狀態(tài)作為sdr_sig模塊輸入。sdr_sig模塊產生面向SDRAM的控制、地址信號。sdr_data模塊實現(xiàn)FPGA與SDRAM之間的數(shù)據(jù)傳輸。sdr_par模塊完成猝發(fā)長度,延時節(jié)拍等參數(shù)設置,通過在該模塊中設置不同的參數(shù)來滿足不同的應用系統(tǒng)。

sdr__top將底層4個模塊整合成1個可以調用的系統(tǒng)。整個IP核類似于黑匣子,不用詳細了解其內部實現(xiàn)細節(jié),只需了解左邊控制信號的含義,對SDRAM的不同操作通過改變左邊控制信號的狀態(tài)即可。

4 結束語

本文提出了基于GAP技術的網(wǎng)絡保護設備設計新方案,闡述了主要模塊的實現(xiàn)方法,限于篇幅不能給出具體細節(jié)和源代碼。采用1個FPGA替代單片機和SCSI協(xié)議控制器,可減少電路數(shù)量,降低成本,便于升級。

評論