基于數據選擇器和D觸發器的多輸入時序電路

在SSI時序邏輯電路設計中,遵循的設計準則是:在保證所設計的時序邏輯電路具有正確功能的前提下,觸發器的激勵函數應最小化,從而簡化電路結構。用卡諾圖法或公式法化簡觸發器的激勵函數,在多輸入變量時相當繁瑣甚至難以進行。因此,需要尋求多輸入時序邏輯電路簡捷設計方法。本文給出多輸入變量時序邏輯網絡的一種新型結構:將D觸發器和數據選擇器進行組合,構成既有存儲功能又有數據選擇功能的多輸入時序網絡,并給出設計過程中不需要進行函數化簡的設計技術。

1 基本原理

1.1 基本多輸入時序網絡

1.1.1 多輸入時序網絡的基本形式

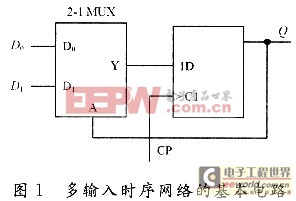

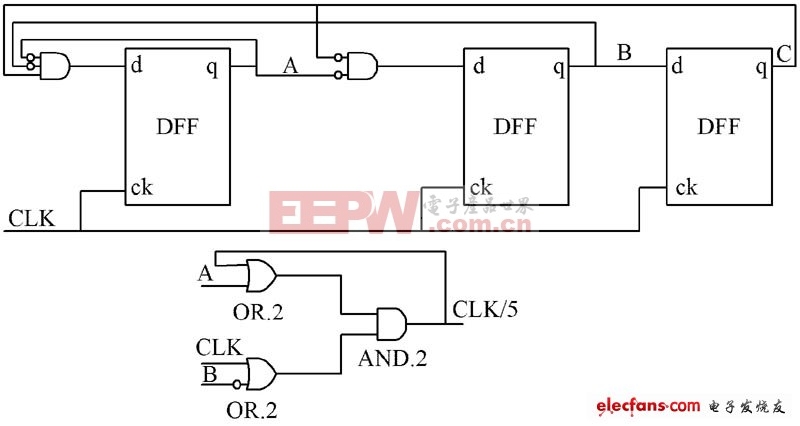

用1個D觸發器和1個2選1數據選擇器構成多輸入時序網絡的基本電路,如圖1所示。

圖1中,觸發器的現態輸出Qn作為數據選擇器的A選擇輸入變量,數據選擇器的Y輸出作為觸發器的D輸入信號,數據選擇器的輸入端D0,D1作為所構成時序網絡的外部信號輸入端。

1.1.2 多輸入時序網絡基本電路的狀態方程

由D觸發器的特性方程Qn+1=D、數據選擇器的輸出邏輯表達式![]() 的關系,得多輸入時序網絡基本電路的狀態方程:

的關系,得多輸入時序網絡基本電路的狀態方程:

![]()

寫成矩陣形式為:

評論