使用用CPLD和Flash實現FPGA的配置

2 具體設計

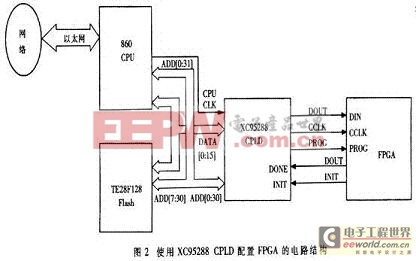

國家數字交換系統工程技術研究中心承擔的國家863項目高性能IPv6核心路由器采用一片Intel E28F128J3A150 16位Flash作為BootFlash對PowerPC2860(MPC860)處理機進行加電配置下載更新的方案,其多余的存儲空間完全可以存放下FPGA所需的配置文件。加電復位、系統啟動后,由處理機與一片XilinxXC95288XL CPLD配合,控制FPGA配置文件從Flash下載到FPGA中,完成對FPGA的配置。860處理機支持網絡功能,當配置文件需要更新時,可通過網絡將新的配置文件發送到處理機,然后再由處理機更新系統中的Flash。采用XC95288CPLD配置FPGA的具體電路設計結構如圖2所示。

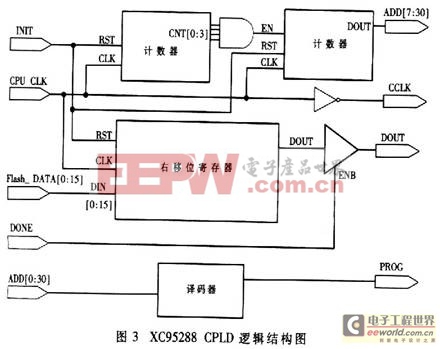

圖2中,CPLD主要功能是把從Flash中讀出的數據轉換成串行輸出,然后再將地址遞增。CCLK(信號由CPU時鐘產生。PROG信號則由CPU輸出的地址數據經譯碼模塊產生。XC95288C PLD邏輯結構如圖3所示。

評論