基于VHDL的線性分組碼編譯碼器的研究設計

則可得由伴隨子S決定對應的錯誤圖樣集e,即為典型監督矩陣的轉置HT,如表1所示。

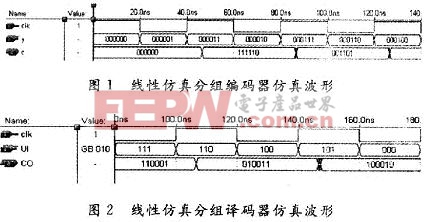

3 仿真及分析

圖1、圖2分別為線性仿真分組編碼器、譯碼器電路的仿真波形。圖中各參數含義如下:clk是系統時鐘信號輸入;UI是編碼器中三位線性分組碼的輸入;CO是編碼器中六位編碼的輸出;Y是解碼器中六位編碼的輸入;c是解碼器中六位譯碼的輸出。

在圖1、圖2中,截取了仿真的部分波形進行分析,產生的六位編碼CO、六位譯碼Y完全依據線性分組碼的編譯碼規則,任意兩個許用碼組之和(逐位模2加)仍為一許用碼組,即具有封閉性。

4 結語

對線性分組碼編、譯碼器的設計基于VHDL(硬件描述語言),與傳統設計相比較,采用VHDL語言設計的線性分組碼編、譯碼器無需考慮具體電路的實現,只需要掌握編譯碼原理,根據相應的編譯碼規則轉換成VHDL語言,大大減少了設計人員的工作量,提高了設計的準確性和效率。程序已在Max+PlusⅡ10.O工具軟件上進行了編譯、仿真和調試。經過實驗結果的分析,說明本設計是正確的。本文給出的設計思想也適用于其他基于PLD芯片的系統設計。

評論