復雜可編程邏輯器件在通信數據傳輸中的應用

1 概述

隨著大規模集成電路和單片機的迅速發展,復雜可編程邏輯器件(CPLD)具有使用靈活、可靠性高、功能強大的優點,在電子產品設計中得到了廣泛的應用。CPLD 可實現在系統編程,重復多次,而且還兼容IEEE1149.1(JTAG)標準的測試激勵端和邊界掃描能力,使用CPLD 器件進行開發,不僅可以提高系統的集成化程度、可靠性和可擴充性,而且大大縮短產品的設計周期。由于CPLD 采用連續連接結構,易于預測延時,從而使電路仿真更加準確。CPLD 是標準的大規模集成電路產品,可用于各種數字邏輯系統的設計。近年來,隨著采用先進的集成工藝和大批量生產,CPLD 器件成本不斷下降,集成密度、速度和性能都大幅度提高,這樣一個芯片就可以實現一個復雜的數字電路系統;再加上使用方便的開發工具,給設計修改帶來很大方便。

實驗室設計開發了一款無線數據接收平臺,上下行速率可以達到1Mbps。射頻部分采用了Maxim 的射頻套片,基帶部分采用了OMAP 平臺,基帶射頻接口采用了ADI 公司的混合信號前端(MxFE?)基帶傳輸芯片AD9861,系統的邏輯控制和數據的緩沖采用了ALTERA 的CPLD EPM240GT100C3。

2 EPM240GT100C3 實現的功能與總體要求

EPM240GT100C3要完成AD9861的時序控制、AD9861和OMAP之間的數據緩存以及提供網口芯片LAN91C93所需的控制信號。在這幾項功能中,最主要的是數據緩存功能。要想正確地實現緩存功能,就必須要求緩存的收發I、Q數據不丟失,不顛倒,不錯相,同時保證數據的先寫后讀。按照這樣的思想,再結合兩邊的接口時序正確地配置讀寫地址、讀寫時鐘,就可以完成所需功能。

3 CPLD 程序的詳細設計

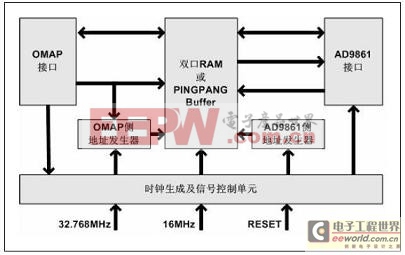

CPLD的主要功能是完成數據緩存和一些時鐘控制信號的產生。其功能框圖如圖1所示,主要包括雙口RAM存儲體單元,時鐘和控制信號產生單元,OMAP側地址發生單元,AD9861側地址發生單元。

圖1 CPLD 功能框圖

3.1 雙口RAM 的設計方法

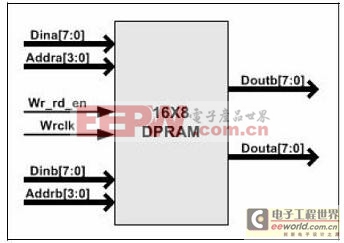

因為OMAP和AD9861兩邊都有讀寫操作,于是選擇了雙口RAM(DPRAM)作為數據的緩存。由于CPLD內部的邏輯資源和布線資源有限,并且沒有獨立的DPRAM區,只能用DFF來完成緩存功能,這就限制了DPRAM的大小。因為系統要求每個DMA中斷讀寫8個數據,為了減小讀寫沖突的可能性,同時盡量地降低FF資源的利用,最終采用了相當于兩個8×8大小乒乓緩沖的16×8雙口RAM緩沖區。DPRAM的外部接口如圖2所示:

圖2 DPRAM 的外部接口

其中dina和douta接OMAP的數據線,dinb和doutb接AD9861的數據線,addra和addrb為內部產生的讀寫地址。Wr_rd_en控制讀寫的方向,和TX_RX相連,即當Wr_rd_en=’1’時,為發射,數據由OMAP寫入,AD讀出,數據流向從dina->doub; 當Wr_rd_en=’0’時,為接收,數據由AD端寫入,AD讀出,數據流向從dinb->doua;wrclk在四種時鐘之間切換,分別為3.2768M,6.4M,75M,84M,由TX_RX和V_D_SEL信號的高低來控制。為了降低布線資源的使用,讀數時沒有用讀時鐘,而是直接把addra和addrb地址上的數據輸出,因為addra和addrb本來就是與讀寫時鐘同步的。

評論