如何通過RTL分析、SDC約束和綜合向導進行FPGA設計

這里的解決方案是在綜合的第一階段(編譯)后截取映射名稱,在 BluePearl 軟件套件的 SDC 生成工具中使用名稱,并為綜合工具的第二階段(優化)提供適當的SDC。該方法給FPGA設計人員提供了一個最佳解決方案,無需花時間處理格式化問題。

能取得哪些實際的效果

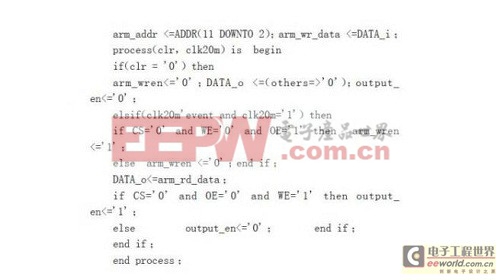

Blue Pearl 軟件套件能實現一些任務的自動化, 設計人員對其結果質量(QoR) 很滿意。表 1 顯示了用 Blue Pearl 軟件套件自動生成SDC,能將示例設計的 QoR 提升 20%,該示例采用多個 IP 核,其中包括 Verilog 的R1200 和 VHDL 的 AES 加密。

對FPGA設計人員來說,降低壓力、簡化工作的一個好辦法就是跟別人一樣添加RTL分析、SDC 生成和綜合向導工具。

評論