向FPGA內植入嵌入式軟核的電容在線測試電路

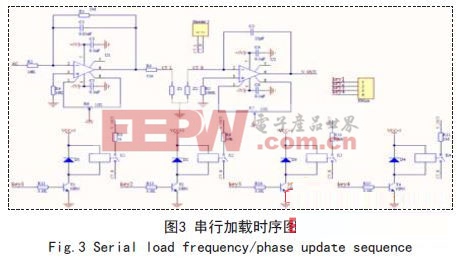

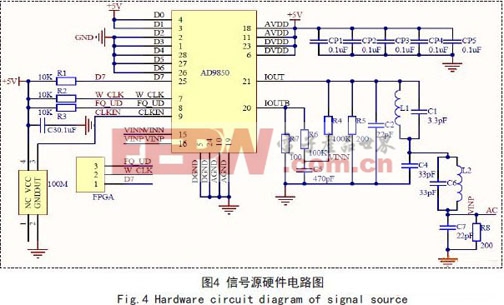

串行輸入方式,在W_CLK上升沿把數據位D7的一位數據串行輸入,當輸入40位后,用一個FQ_UD脈沖即可更新輸出頻率和相位。圖4為DDS硬件電路圖。本文引用地址:http://cqxgywz.com/article/226816.htm

串行輸入方式,在W_CLK上升沿把數據位D7的一位數據串行輸入,當輸入40位后,用一個FQ_UD脈沖即可更新輸出頻率和相位。圖4為DDS硬件電路圖。本文引用地址:http://cqxgywz.com/article/226816.htm

其中,D0~D7為八位數據輸入端口,給內部寄存器裝入40位控制數據,本文采用串行輸入,所以只用到D7位與FPGA相連;CLKIN為外部參考時鐘輸入,本設計采用100M外部時鐘輸入;W_CLK為字輸入信號,上升沿有效;FQ_UD為頻率更新控制信號,時鐘上升沿確認輸入數據有效;VINP和VINN分別為內部比較器的正負輸入端;IOUT為內部DAC輸出端;IOUTB為“互補”DAC輸出端;AVDD和DVDD采用+5V供電。IOUT輸出信號經過濾波器后作為測試電路的激勵信號。

4.測試結果與結論

經過上述系統設計,試驗測得的結果如表1所示。

結果中*表示數據不停變化或者結果超出量程。

通過上述實測值與標準值的比較可以看出本文設計的由FPGA控制的電容在線測試系統具有多量程自動選擇,測試精度高,使用方便等特點,測試范圍達到0.01μF~3μF.經理論分析和試驗證明,該設計具有很強的實用性和可靠性。

電容的相關文章:電容屏和電阻屏的區別

電容屏相關文章:電容屏原理

評論